# Modelling and Performance Analysis of OpenFlow Switches in Software-Defined Networking

by

Deepak Kumar Singh

A thesis

submitted to the Victoria University of Wellington

in fulfilment of the

requirements for the degree of

Doctor of Philosophy

in Network Engineering.

Victoria University of Wellington 2019

### **Abstract**

Software-Defined-Networking (SDN) simplifies the configuration complexity in the computer communication network by decoupling the control plane from the data plane in a switch. In SDN, the switch has the data plane only and is configured by the logically centralised controller which simplifies the forwarding of packets in the network. However, an SDN switch is sensitive to delay and loss of packets which significantly affects the network performance.

This thesis uses queueing theory to conduct modelling and performance analysis of OpenFlow-based SDN switches. OpenFlow is the defacto protocol for communication between an SDN switch and the controller. Using queueing theory, three aspects of packet processing in an SDN switch are explored. First, the existing research has primarily modelled the output buffer of an SDN switch using two buffer sharing mechanisms: the single shared buffer and the priority buffer. However, the effect of buffer dimensioning in these buffer sharing mechanisms has not been investigated. Buffer dimensioning helps in determining the minimum buffer capacity for a desired loss probability. The research in this thesis shows that the use of priority buffer in an SDN switch reduces the time to update flow tables than the shared buffer but at the cost of a higher buffer capacity.

Second, much of the existing research has not investigated the impact of internal buffering of data packets whereby a fraction of a data packet header is sent to the controller instead of an entire data packet. To investigate the impact of internal buffering, the queueing model for an SDN switch with the internal buffer is developed. The investigation shows that at the time of congestion, the internal buffer in an SDN switch improves the network performance with lower delay and lower packet loss.

Finally, existing research has focused on a software switch in SDN and very little research has studied the performance of a hardware switch. To characterise the performance of SDN-based hardware and software switches and identify the tradeoffs between them, a unified queueing model has been developed. The unified queueing model is an analytical tool for network engineers to predict delay and packet loss in their SDN deployments. The analysis shows the benefits of a hardware switch over a software switch. These benefits are lower delay and lower packet loss. However, the increasing involvement of the controller reduces the benefit of using a hardware switch, i.e. forwarding packets at the line speed rate.

This research guides network designers and analysts in the selection of the shared or buffer model for an SDN switch for their desired Quality of Service (QoS). Furthermore, the developed queueing model for an SDN switch with the internal buffer studies the impact of internal buffering in an SDN switch. Finally, the unified queueing model helps in the selection of a software or hardware switch in SDN.

# Acknowledgments

I would like to express my deep gratitude to my supervisors Dr. Bryan Ng and Professor Winston Seah for their exemplary guidance, monitoring and constant encouragement throughout the progress of my thesis. I would like to extend my gratitude to Professor Yuan-Chen Lai and Professor Ying-Dar Lin for their informative suggestions and motivation for my hard work.

I also take this opportunity to express my gratitude to Dr. Ying Qu, Dr. Hang Yu, Dr. Liang Yang, Dr. Adrian Pekar, Kirsten Reid, Jakob Pfender, and Jordan Ansell for their cordial support, valuable information and guidance, which helped me in my research activities through various stages.

I am obliged to my colleagues for their cooperation during the period of my stay. Lastly, I thank almighty, my parents, sister Annu, and brother-in-law Nikhil for their constant encouragement throughout my study.

## **Publications**

- Deepak Singh, Bryan Ng, Y.C. Lai, Y.D. Lin and Winston K.G. Seah, 'Modelling Software-Defined Networking: Switch Design with Finite Buffer and Priority Queueing', Proceedings of the 42nd IEEE Conference on Local Computer Networks (LCN), October 9-12, 2017, Singapore.

- Deepak Singh, Bryan Ng, Y.C. Lai, Y.D. Lin and Winston K.G. Seah, 'Modelling Switches with Internal Buffering in Software-Defined Networks', Proceedings of the 27th International Conference on Computer Communication and Networks (ICCCN 2018), July 30 -August 2, 2018, Hangzhou, China.

- Deepak Singh, Bryan Ng, Y.C. Lai, Y.D. Lin and Winston K.G. Seah, Modelling Software-Defined Networking: Software and Hardware Switches, *Journal of Networking and Computer Applications*, Vol 122, 15 Nov 2018.

- Deepak Singh, Bryan Ng, Y.C. Lai, Y.D. Lin and Winston K.G. Seah, Analytical modelling of Software and Hardware Switches with Internal Buffer in Software-Defined Networks, accepted by the *Journal* of Networking and Computer Applications, 18 March 2019.

- **Deepak Singh**, Bryan Ng, Y.C. Lai, Y.D. Lin and Winston K.G. Seah, Encapsulation vs. Internal Buffering: Performance Analysis of OpenFlow-Based Hardware Switch, *submitted* to *IEEE Transactions on Network* and Service Management, 17 Feb 2019.

# **Contents**

| Li | st of 1 | Figures | }           |                               | X    |

|----|---------|---------|-------------|-------------------------------|------|

| Li | st of ' | Tables  |             |                               | xiii |

| 1  | Intr    | oductio | n           |                               | 1    |

|    | 1.1     | Motiv   | ation       |                               | . 3  |

|    | 1.2     | Resea   | rch Challe  | nges                          | . 5  |

|    | 1.3     | Resea   | rch Goals   |                               | . 6  |

|    | 1.4     | Contr   | ibutions .  |                               | . 7  |

|    | 1.5     | Thesis  | Outline .   |                               | . 9  |

| 2  | Bacl    | kgroun  | d and Rel   | ated Work                     | 10   |

|    | 2.1     | SDN:    | Overview    |                               | . 10 |

|    | 2.2     | Packe   | t processir | ng in an SDN switch           | . 14 |

|    |         | 2.2.1   | Buffer sh   | aring mechanism               | . 15 |

|    |         | 2.2.2   | Packet er   | ncapsulation at an SDN switch | . 16 |

|    |         | 2.2.3   | SDN swi     | tch types                     | . 17 |

|    | 2.3     | Appro   | oaches for  | performance analysis          | . 18 |

|    |         | 2.3.1   | Experime    | ental testbeds                | . 19 |

|    |         | 2.3.2   | Software    | -based tools                  | . 20 |

|    |         | 2.3.3   | Mathema     | atical models                 | . 21 |

|    |         |         | 2.3.3.1     | Network Calculus              | . 21 |

|    |         |         | 2.3.3.2     | Queueing theory               | . 23 |

viii *CONTENTS*

|   |      | 2.3.4   | Quasi-B     | irth-Death process                           | 27 |

|---|------|---------|-------------|----------------------------------------------|----|

|   |      |         | 2.3.4.1     | Homogenous QBD process                       | 28 |

|   |      |         | 2.3.4.2     | Nonhomogenous QBD process                    | 30 |

|   | 2.4  | Relate  | ed works    | on queueing models for an SDN Switch         | 31 |

|   |      | 2.4.1   | Buffer s    | haring models                                | 32 |

|   |      | 2.4.2   | Internal    | buffering                                    | 36 |

|   |      | 2.4.3   | SDN sw      | itches: Software vs. Hardware                | 40 |

|   | 2.5  | Summ    | nary        |                                              | 43 |

| 3 | Sha  | red vs. | Priority l  | Buffer                                       | 45 |

|   | 3.1  | Infinit | e and fini  | ite capacity queue models                    | 45 |

|   | 3.2  | Buffer  | dimensi     | oning with queueing models                   | 46 |

|   | 3.3  | SDN s   | switch de   | sign guidelines through comparative analysis | 48 |

|   |      | 3.3.1   | Model S     | E: an SDN switch with a single shared queue  | 49 |

|   |      |         | 3.3.1.1     | Generator matrix                             | 50 |

|   |      |         | 3.3.1.2     | Network performance metrics for SE           | 52 |

|   |      | 3.3.2   | Model S     | SPE: an SDN Switch with a two-priority queue | 55 |

|   |      |         | 3.3.2.1     | Generator matrix                             | 56 |

|   |      |         | 3.3.2.2     | Network performance metrics for SPE          | 58 |

|   |      | 3.3.3   | Buffer d    | imensioning: SE vs. SPE                      | 61 |

|   | 3.4  | Result  | ts          |                                              | 62 |

|   |      | 3.4.1   | Validati    | ng queueing models SE and SPE                | 63 |

|   |      | 3.4.2   | Switch o    | design considerations                        | 65 |

|   |      |         | 3.4.2.1     | Relative minimum capacity                    | 65 |

|   |      |         | 3.4.2.2     | Relative average time to install FTE         | 67 |

|   | 3.5  | Concl   | usion       |                                              | 70 |

|   | 3.6  | Summ    | nary        |                                              | 70 |

| 4 | Inte | rnal Bu | ıffering i  | n SDN Switches                               | 72 |

|   | 4.1  | Mode    | l SPI: an S | SDN Switch with the internal buffer          | 73 |

|   |      | 4.1.1   | Generat     | or matrix                                    | 77 |

|   |      | 4.1.2   | Networ      | k performance metrics for SPI                | 80 |

| CONTENTS | ix |

|----------|----|

|          |    |

|   |     | 4.1.3 | Buffer d   | imensioning for SPI                           | 83  |

|---|-----|-------|------------|-----------------------------------------------|-----|

|   | 4.2 | Resul | ts         |                                               | 83  |

|   |     | 4.2.1 | Validati   | ng queueing model SPI                         | 85  |

|   |     | 4.2.2 | SPE vs.    | SPI                                           | 86  |

|   |     |       | 4.2.2.1    | Relative minimum buffer capacity              | 86  |

|   |     |       | 4.2.2.2    | Relative average delay                        | 87  |

|   |     |       | 4.2.2.3    | Relative average packet loss probability      | 89  |

|   |     | 4.2.3 | Increasi   | ng packet arrivals ( $\lambda_1$ ): $\ldots$  | 90  |

|   | 4.3 | Concl | usion      |                                               | 94  |

|   | 4.4 | Sumn  | nary       |                                               | 94  |

| 5 | Har | dware | Switching  | g in SDN Switches                             | 95  |

|   | 5.1 | Mode  | l HPE: a l | nardware switch without the internal buffer . | 97  |

|   |     | 5.1.1 | Generat    | or matrix                                     | 99  |

|   |     | 5.1.2 | Networ     | k performance metrics for HPE                 | 103 |

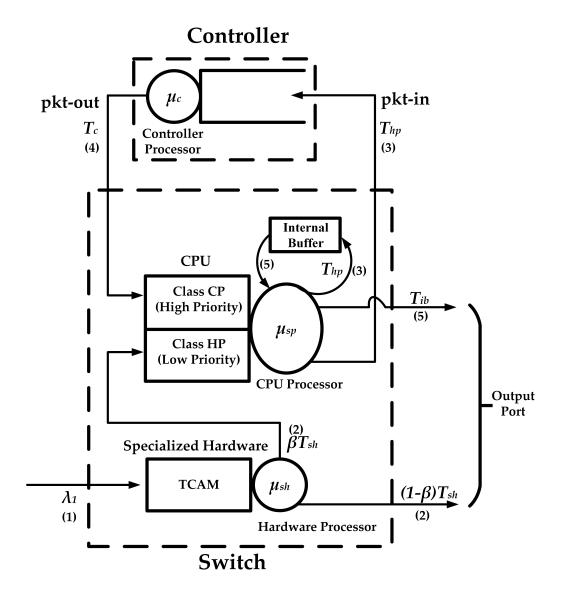

|   | 5.2 | Mode  | l HPI: a h | ardware switch with the internal buffer       | 106 |

|   |     | 5.2.1 | Generat    | or matrix                                     | 110 |

|   |     | 5.2.2 | Networ     | k performance metrics for HPI                 | 116 |

|   |     | 5.2.3 | Buffer d   | imensioning for HPE and HPI                   | 118 |

|   | 5.3 | Resul | ts         |                                               | 120 |

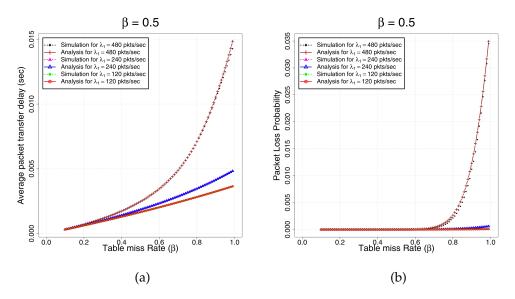

|   |     | 5.3.1 | Validati   | ng queueing models HPE & HPI                  | 121 |

|   |     | 5.3.2 | Software   | e vs. Hardware switch                         | 123 |

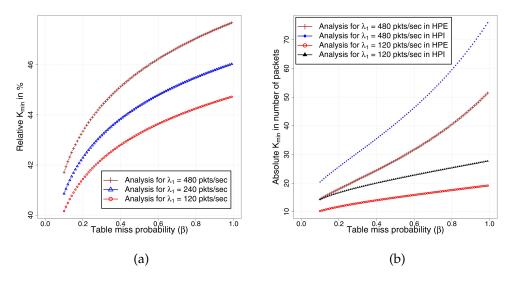

|   |     |       | 5.3.2.1    | Relative minimum buffer capacity              | 123 |

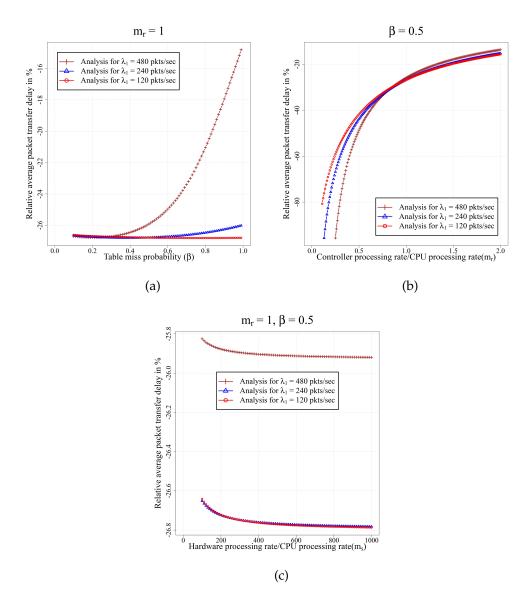

|   |     |       | 5.3.2.2    | Relative average delay                        | 125 |

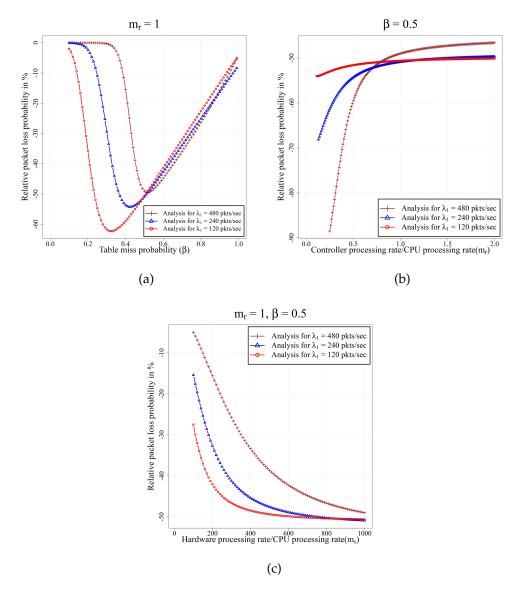

|   |     |       | 5.3.2.3    | Relative average packet loss probability      | 127 |

|   |     | 5.3.3 | HPE vs.    | HPI                                           | 130 |

|   |     |       | 5.3.3.1    | Relative minimum buffer capacity              | 130 |

|   |     |       | 5.3.3.2    | Relative average delay                        | 131 |

|   |     |       | 5.3.3.3    | Relative average packet loss probability      | 134 |

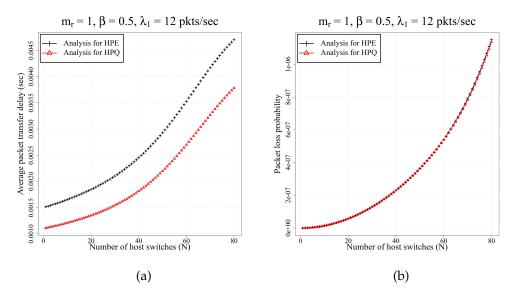

|   |     |       | 5.3.3.4    | Effect of varying number of hosts connected   |     |

|   |     |       |            | to switch                                     | 136 |

| x | CONTENT |

|---|---------|

|   |         |

|   | 5.4  | Conclusion                             | 137 |

|---|------|----------------------------------------|-----|

|   | 5.5  | Summary                                |     |

| 6 | Con  | clusions                               | 140 |

|   | 6.1  | Contributions                          | 141 |

|   | 6.2  | Future Work                            | 142 |

| A | Loga | arithmic Reduction (LR) Method         | 161 |

| В | Mat  | rix Continued Fraction Algorithm (MCF) | 163 |

| C | Mor  | nte Carlo Simulation for Model SE      | 164 |

| D | Mor  | nte Carlo Simulation for Model SPE     | 171 |

| E | Mor  | nte Carlo Simulation for Model SPI     | 177 |

| F | Mor  | nte Carlo Simulation for Model HPE     | 183 |

| G | Mor  | nte Carlo Simulation for Model HPI     | 189 |

# **List of Figures**

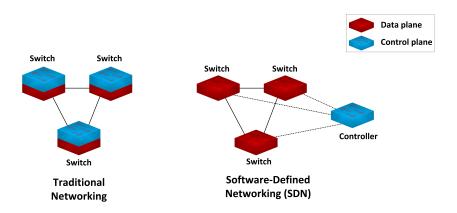

| 2.1 | Comparison between traditional networking architecture and                              |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | SDN                                                                                     | 11 |

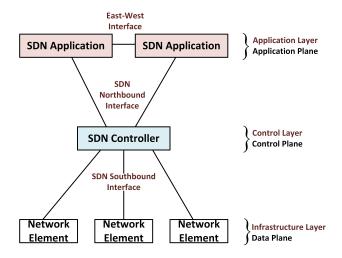

| 2.2 | The components of a typical SDN                                                         | 12 |

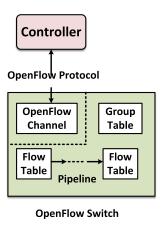

| 2.3 | OpenFlow-based SDN architecture with one controller and                                 |    |

|     | one switch                                                                              | 14 |

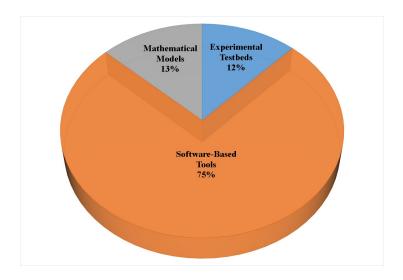

| 2.4 | Approaches for performance analysis in SDN                                              | 19 |

| 2.5 | Generic model for an SDN network                                                        | 32 |

| 2.6 | OpenFlow switch with support for internal buffering [1]                                 | 37 |

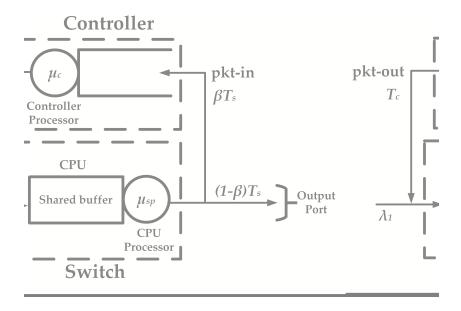

| 3.1 | Model SE – an SDN Switch with a single shared queue                                     | 49 |

| 3.2 | Model SPE – an SDN switch with a two-priority queue                                     | 55 |

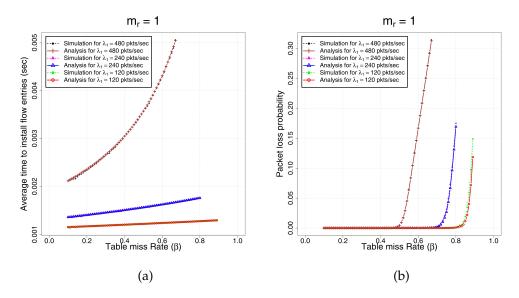

| 3.3 | Validation of Model SE in terms of (a) Average time to in-                              |    |

|     | stall FTE, and (b) Packet loss probability.                                             | 64 |

| 3.4 | Validation of Model SPE in terms of (a) Average time to in-                             |    |

|     | stall FTE, and (b) Packet loss probability.                                             | 64 |

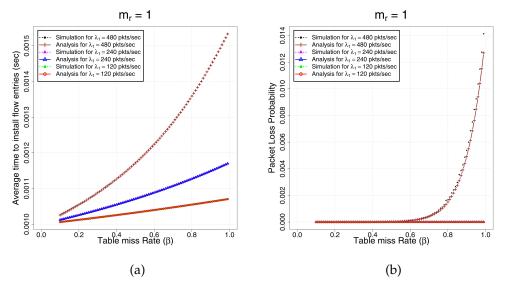

| 3.5 | Minimum switch queue capacity ( $K_{min}$ ) between SE and                              |    |

|     | SPE for $\mu_{sp}=1000$ pkts/sec and increasing $\beta$ : (a) Relative                  |    |

|     | difference i.e. $\epsilon_K$ and (b) Absolute value                                     | 66 |

| 3.6 | Relative time to install FTEs between SE and SPE i.e. $\epsilon_t$ for                  |    |

|     | increasing $\beta$ : (a) $m_r = 0.5$ ; (b) $m_r = 1.0$ ; (c) $m_r = 2.0$                | 68 |

| 3.7 | Relative time to install FTEs between SE and SPE i.e. $\epsilon_{tt}$ for               |    |

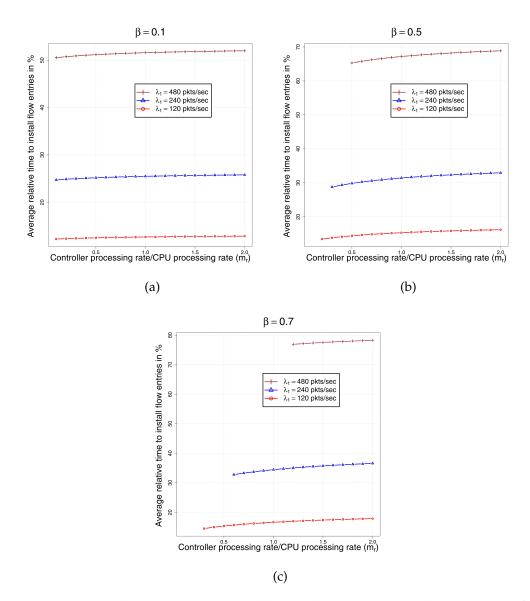

|     | increasing $m_r$ : (a) $\beta = 0.1$ ; (b) $\beta = 0.5$ ; (c) $\beta = 1. \dots \dots$ | 69 |

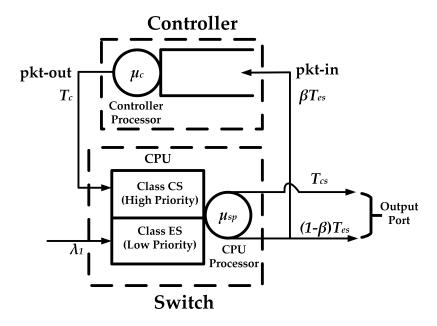

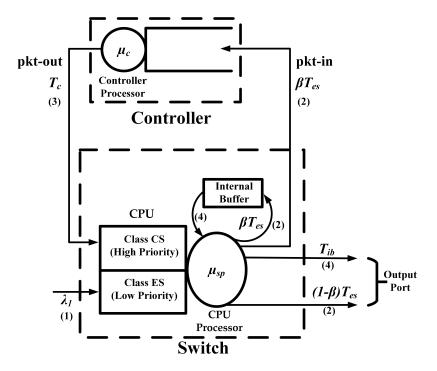

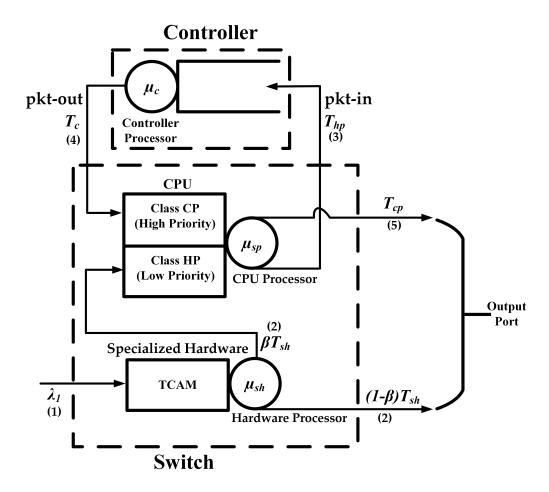

| 4.1 | Model SPI – an SDN switch with a priority queue and the internal buffer                                                                                                              | 74  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

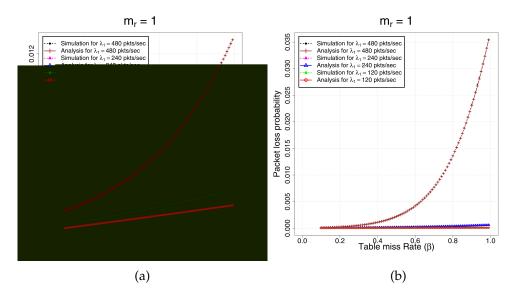

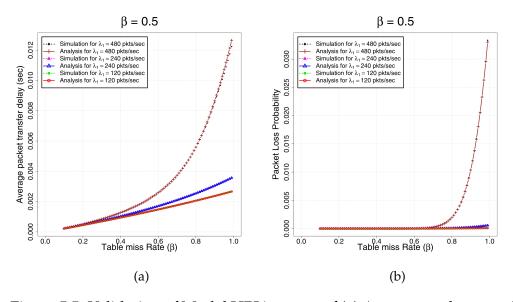

| 4.2 | Validation of Model SPI in terms of (a) Average packet transfer delay, and (b) Packet loss probability.                                                                              | 85  |

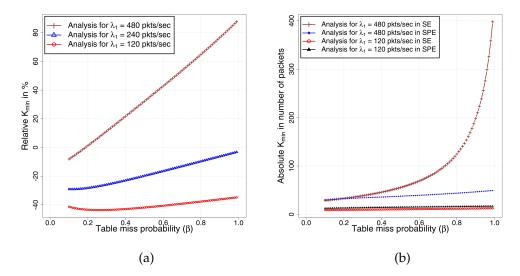

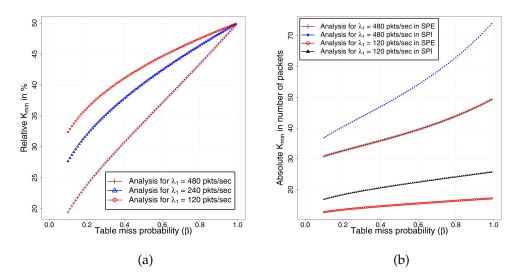

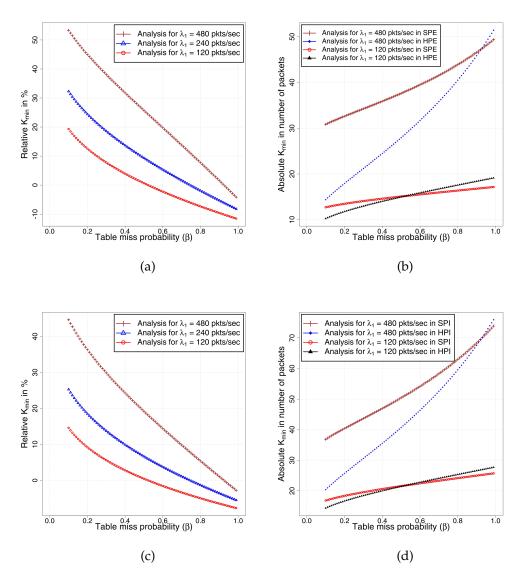

| 4.3 | Minimum switch queue capacity $(K_{min})$ between SPE and SPI for $\mu_{sp}=1000$ pkts/sec and increasing $\beta$ : (a) Relative difference i.e. $\epsilon_K$ and (b) Absolute value | 86  |

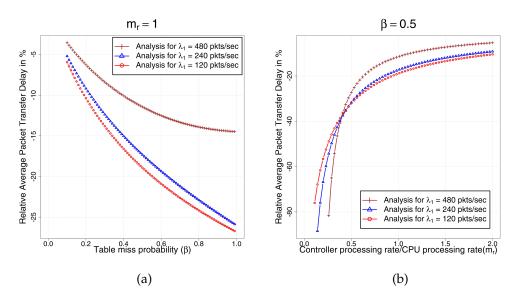

| 4.4 | Relative average packet transfer delay between SPE and SPI i.e. $\epsilon_t$ for (a) increasing $\beta$ and $m_r=1$ ; and (b) increasing $m_r$ and $\beta=0.5.$                      | 87  |

| 4.5 | Relative average packet loss probability between SPE and SPI i.e. $\epsilon_t$ for (a) increasing $\beta$ and $m_r = 1$ ; and (b) increasing $m_r$ and $\beta = 0.5$                 | 89  |

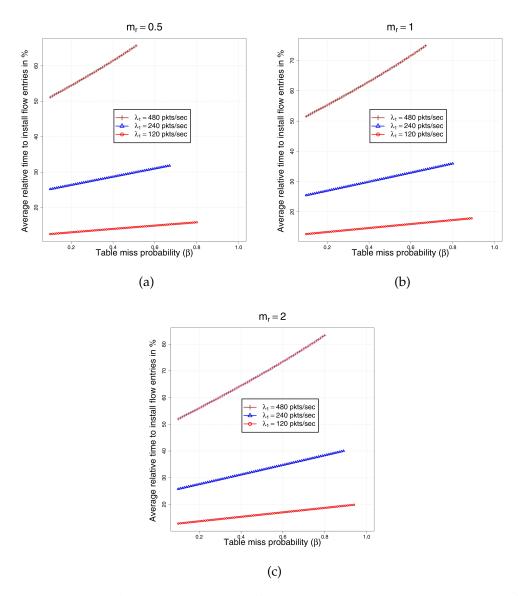

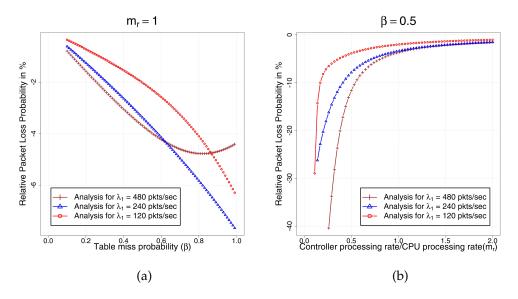

| 4.6 | Relative average packet transfer delay between SPI and SPE for varying $\lambda_1$ with (a) $m_r=0.5$ ; (b) $m_r=1$ ; and (c) $m_r=2$ .                                              | 91  |

| 4.7 | Relative average packet loss probability between SPE and SPI for varying $\lambda_1$ with (a) $m_r = 0.5$ ; (b) $m_r = 1$ ; and (c) $m_r = 2$                                        | 93  |

| 5.1 | Generic model for a hardware-based SDN switch with the specialised hardware and the CPU                                                                                              | 96  |

| 5.2 | Model HPE – hardware switch modelled with two servers to reflect the presence of network processing functions                                                                        | 98  |

| 5.3 | Model HPI – hardware switch modelled with two servers and internal buffer to realise the internal buffering                                                                          | 107 |

| 5.4 | Validation of Model HPE in terms of (a) Average packet transfer delay, and (b) Packet loss probability                                                                               | 122 |

| 5.5 | Validation of Model HPI in terms of (a) Average packet transfer delay, and (b) Packet loss probability.                                                                              | 122 |

| 5.6  | Minimum switch queue capacity $(K_{min})$ (a) Relative differ-                                 |     |

|------|------------------------------------------------------------------------------------------------|-----|

|      | ence between SPE and HPE i.e. $\epsilon_{Ka}$ , (b) Absolute value be-                         |     |

|      | tween SPE and HPE, (c) Relative difference between SPI and                                     |     |

|      | HPI i.e. $\epsilon_{Kb}$ and (d) Absolute value between SPI and HPI for                        |     |

|      | $\mu_{sp} = 1000 \text{ pkts/sec}$ and increasing $\beta$                                      | 124 |

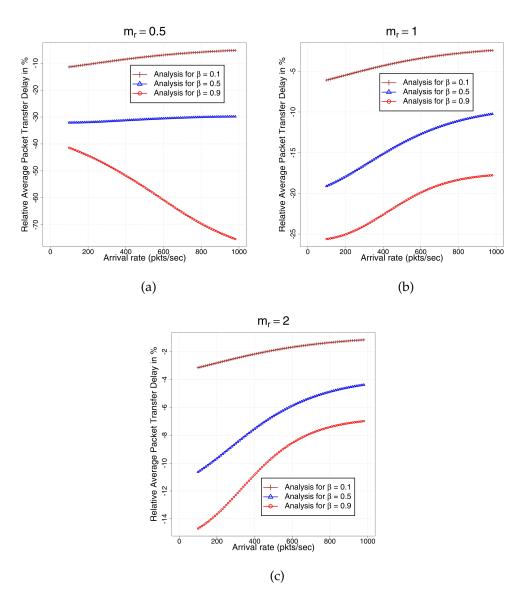

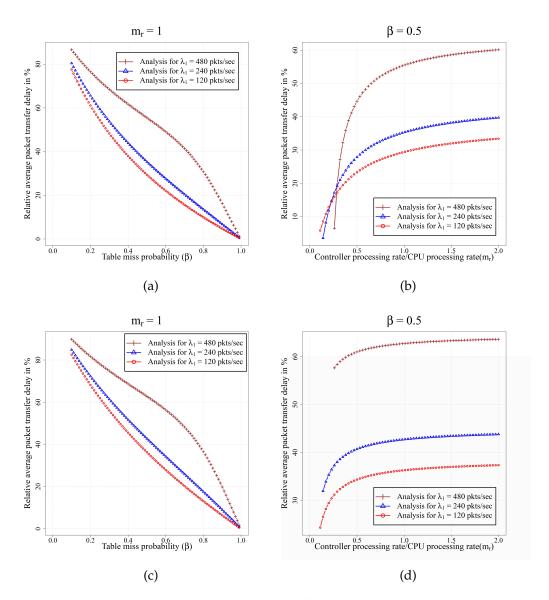

| 5.7  | Relative average packet transfer delay between (a – b) SPE                                     |     |

|      | and HPE in % i.e. $\epsilon_{da}$ , (c – d) SPI and HPI in % i.e. $\epsilon_{db}$ for          |     |

|      | increasing $\beta$ and $m_r$                                                                   | 126 |

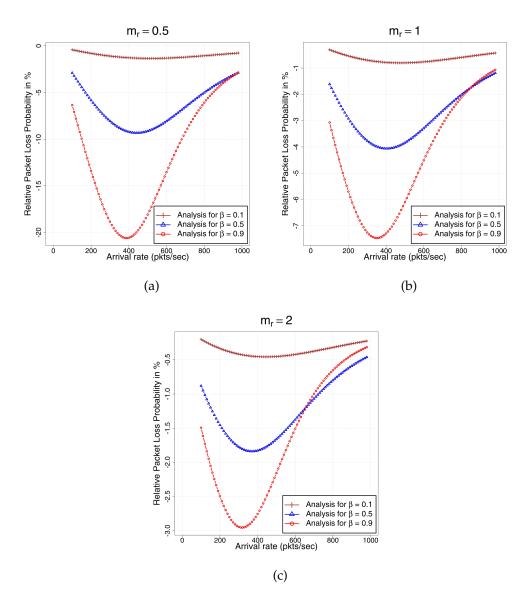

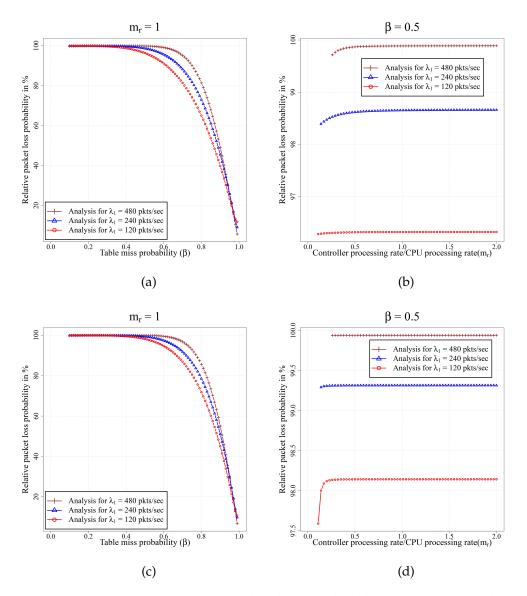

| 5.8  | Relative average packet loss probability between (a – b) SPE                                   |     |

|      | and HPE i.e. $\epsilon_{la}$ , (c – d) SPI and HPI i.e. $\epsilon_{lb}$ for increasing $\beta$ |     |

|      | and $m_r$                                                                                      | 128 |

| 5.9  | Minimum switch queue capacity ( $K_{min}$ ) between HPE and                                    |     |

|      | HPI for $\mu_{sp}=1000$ pkts/sec and increasing $\beta$ : (a) Relative                         |     |

|      | difference i.e. $\epsilon_{Kc}$ and (b) Absolute value                                         | 131 |

| 5.10 | Relative average packet transfer delay between HPE and                                         |     |

|      | HPI i.e. $\epsilon_{dc}$ for (a) increasing $\beta$ and $m_r=1$ , $m_s=1000$ ;                 |     |

|      | (b) increasing $m_r$ and $\beta=0.5$ , $m_s=1000$ ; and (c) increasing                         |     |

|      | $m_s$ and $m_r = 1$ , $\beta = 0.5$                                                            | 132 |

| 5.11 | Relative average packet loss probability between HPE and                                       |     |

|      | HPI i.e. $\epsilon_t$ for (a) increasing $\beta$ and $m_r=1$ , $m_s=1000$ ; (b)                |     |

|      | increasing $m_r$ and $\beta=0.5$ , $m_s=1000$ ; and (c) increasing $m_s$                       |     |

|      | and $m_r = 1$ , $\beta = 0.5$                                                                  | 135 |

| 5.12 | Effect of varying number of hosts for $\lambda_1 = 12$ pkts/sec,                               |     |

|      | $m_r=1$ and $\beta=0.5$                                                                        | 138 |

# **List of Tables**

| 2.1 | Related works on SDN modelling using Network Calculus      | 23  |

|-----|------------------------------------------------------------|-----|

| 2.2 | Related works on SDN modelling using Queueing Theory       | 26  |

| 2.3 | Summary of queueing models for buffer sharing mechanisms.  | 35  |

| 2.4 | Summary of queueing models for packet encapsulation meth-  |     |

|     | ods at the SDN switch                                      | 40  |

| 2.5 | Summary of queueing models for SDN switches                | 43  |

| 3.1 | Permissible transitions for Model SE                       | 51  |

|     |                                                            |     |

| 3.2 | Permissible transitions for Model SPE                      | 57  |

| 3.3 | Parameter used for analysis and simulation for both SE and |     |

|     | SPE                                                        | 63  |

| 4.1 | Permissible Transitions for Model SPI                      | 76  |

| 4.2 | Parameter used for analysis and simulation for both SPE    |     |

|     | and SPI                                                    | 84  |

| 5.1 | Permissible transitions for Model HPE                      | 100 |

| 5.2 | Permissible Transitions for Model HPI                      | 109 |

| 5.3 | Parameter used for analysis and simulation for both HPE    |     |

|     | and HPI                                                    | 121 |

# Chapter 1

### Introduction

A switch/router in a computer communication network is a networking device that primarily forwards packets. In traditional networking, a switch/router has a control plane and data plane coupled together [2]. The control plane performs control functions such as routing protocols and middle-box configuration while the data plane forwards packets based on decisions made by the control plane. This makes the control function hardware-dependent in the traditional network resulting in a complex network configuration. In addition, the use of a low-level programming language and vendor dependency makes it difficult for network operators during configuration. To simplify the configuration complexity in the traditional network, a new networking paradigm called Software-Defined Networking (SDN) that uses a high-level programming language has emerged [3].

SDN is a network paradigm in which the control plane is decoupled from a switch/router. In an SDN, the control function is moved to a logically centralised controller which eases the load on a switch/router with the primary function of forwarding packets. It allows the network to be controlled and managed through a software written in a high-level programming language. The shift of control function from a hardware to software dependency allows the system to be more agile, programmable

and centrally managed. This makes SDN a promising approach for future networks and services such as Software-Defined Wireless Access Network (SDWAN) [5], 5G mobile networks [6], Industrial Internet of Things (IIoT) [7], Software-Defined Information Centric Network (ICN) [8], and Software-Defined Smart Home [9]. The concept of an SDN is realised with OpenFlow which is among the first and most widely used specification to define communication between the controller and switch in an SDN paradigm [4].

SDN is a promising network paradigm which overcomes limitations of the traditional network [10]. However, research into identifying the potential bottlenecks of an SDN is still being conducted to improve the overall performance of an SDN. The performance issues for packet processing in an SDN switch that require further study and investigation are buffer sharing mechanisms, packet encapsulation methods, and SDN switch types. There are various buffer sharing models which need to be compared and analysed to address design challenges such as provisioning of buffer capacity and protection of control packets in an SDN switch [11, 12]. Similarly, there are provisions in OpenFlow for various packet encapsulation methods at an SDN switch which are still unexplored [13]. These encapsulation methods for processing data packets at SDN switch need to be studied and analysed to provide insights and guidelines to network analysts. Finally, SDN switches are generally categorised into software switches and hardware switches [14]. These switches need to be compared to develop guidelines that can be used during SDN deployment.

The performance analysis of an SDN has been done by simulations, measurements or experimental testbeds, and analytical models [2, 15]. While simulations and experimental testbeds have their own advantages, analytical models can be used to verify and authenticate simulated or experimental results [16, 17]. Analytical modelling of an SDN switch provides important insights for benchmarking switch performance and parametric sensitivity analysis to help network engineers identify critical fac-

3

tors that may influence network performance.

This thesis contributes to analytical modelling and performance analysis of a reactive SDN architecture using queueing theory. It investigates different aspects of packet processing in an SDN switch. The outcomes for these aspects will help network designers and analysts to achieve the desirable network performance.

### 1.1 Motivation

Analytical models of an SDN switch are a key step for SDN performance characterisation. These models will help network engineers design networks suitable for delay and packet loss sensitive applications like industrial automation systems, interactive video, network gaming, VoIP, and online surgery [18, 19, 20, 21]. Analytical models can be used in validating experimental or simulated results with the theoretical support in the form of mathematical expressions, theorems and proofs. They have the advantage of being a cheaper and faster approaches for performance analysis than experimental testbeds and simulations.

In an SDN switch, the control traffic feedback by the controller carries important flow updates. The choice of buffer sharing mechanisms for an SDN switch for the protection of flow updates has a significant impact on the overall performance of an SDN [11, 12]. Therefore, the selection of an appropriate buffer sharing mechanism that can provide protection to flow updates and accurately capture SDN behaviour need to be studied. Generally, there are two buffer sharing mechanisms used for an SDN switch which are: *shared buffer model* and *priority buffer model*. The shared buffer model is the usual assumption for an SDN switch with a single shared buffer for both control traffic and external data traffic arriving at the switch. On the other hand, the priority buffer model uses a high priority class for the control traffic and low priority class for the data traffic [11]. Clearly, the priority buffer model provides protection to the flow updates

but its effect on the overall performance of an SDN remains unclear. A comparative analysis between the shared and priority buffer models will guide switch designers in their SDN deployments.

Similarly, the data packet in a flow that arrives at the switch may not have matching flow table entries is sent to the controller. Based on the OpenFlow specification [13], the data packet seeking a flow update from the controller can be processed via three packet encapsulation methods: full encapsulation, internal buffering, and partial encapsulation. With the full encapsulation method, the entire data packet is encapsulated and sent to the controller. Whereas in the internal buffering method, the data packet is temporarily buffered and a fraction of the data packet is only encapsulated. In the partial encapsulation method, if there is sufficient memory to buffer packets, the internal buffering method is used otherwise the full encapsulation method is used. The full encapsulation method is the default packet processing method and is widely used for SDN switches [1]. Consequently, the remaining encapsulation methods, the internal buffering and partial encapsulation methods have not been explored much. The selection of a packet encapsulation method at an SDN switch also affects the overall performance of an SDN that need to be studied and investigated. Therefore, the comparative analysis between these packet encapsulation methods will guide network analysts to obtain the best performance during their SDN deployments.

Lastly, unlike traditional networking, an SDN switch can also be categorised as a software or hardware switch. A software-based SDN switch is a virtual switch such that is instantiated in a virtual machine, whereas a hardware-based SDN switch is a physical switch [4]. A hardware switch processes the incoming packets at the line speed rate but is resource constraint due to the cost, size and energy consumption. On the other hand, a software switch is cheaper, consumes less power, is scalable and offers flexibility to implement complex actions but at the cost of slower performance [14]. Both software and hardware switches have strengths and

5

weaknesses. Therefore, more research needs to be conducted into why one could be selected rather than other to achieve an optimal performance in an SDN.

Through research in analytical modelling using queueing theory, realistic queueing models for an SDN are expected that will represent SDN behaviour accurately and help in understanding various aspects of an SDN switch through performance analyses. These models will guide switch designers and network analysts in their SDN deployments.

### 1.2 Research Challenges

Modelling and performance analysis of an SDN switch come with the challenges that are attributed to the characteristics of an SDN and limitations of analytical models. The research challenges associated with the modelling and performance analysis of an SDN switch in this thesis are listed below:

- Estimation of a cost-effective buffer capacity for an SDN switch. Buffer dimensioning helps in estimating the minimum buffer capacity for the switch such that packet loss in the switch is no more than a desired link loss rate. However, buffer dimensioning estimates the buffer capacity based on parameters such as the arrival rate, the service rate, and the server utilisation. The estimated buffer capacity may not be cost-effective and feasible for the desired loss probability. Therefore, buffer dimensioning for different buffer sharing mechanisms should consider the trade-off between Quality of Service (QoS) and the cost factor.

- Modelling of an SDN switch with the internal buffer. With internal buffering in an SDN switch, the forwarding delay of packets can be decreased [106], Quality of Service can be improved with reduced

- packet loss [122], and bandwidth of the control channel can be optimised [1]. However, internal buffering requires sufficient memory which is not feasible in low-end SDN switches. Therefore, modelling of an SDN switch with the internal buffer needs to assume that the switch has sufficient memory to characterise internal buffering.

- Modelling of a hardware-based SDN switch. A hardware switch maintains a software flow table in the central processing unit (CPU) and a hardware flow table in the specialised hardware for forwarding of packets. The software and hardware flow tables are synchronised through a middleware layer on the switch to avoid duplicate entries and to ensure consistent forwarding behaviour. However, it is difficult to characterise the synchronisation between software and hardware flow tables in a hardware switch. Therefore, modelling of a hardware-based SDN switch requires assumption that the CPU synchronises the flow tables with the specialised hardware.

### 1.3 Research Goals

The associated research goals are as follows:

- To provide guidelines to switch designers that include selection criteria for different buffering strategies and the minimum buffer capacity for the desired loss probability. This goal aims at modelling the output buffer of an SDN switch using queueing theory where external and internal traffic arrives at the switch. The two main objectives of this goal are: (i) to compare existing buffer sharing models and (ii) to perform buffer dimensioning for informing switch design.

- To provide insights to network analysts for the use of internal buffering in an SDN with the prediction of performance measures

7

such as the delay and packet loss. This goal aims to use queueing theory to derive a first-order estimate of an SDN switch performance and to identify potential trade-offs between switch designs with and without the internal buffer. This goal is to develop the queueing model to study internal buffering in an SDN switch. The two main objectives of this goal are (a) to investigate the effect of the internal buffer in the performance of an SDN switch with the help of a queueing model, and (b) to compare the queueing models for an SDN switch with and without internal buffer, and hence identify the trade-offs.

• To provide guidelines to network engineers for deployment choices such as under what operating conditions a software data plane outperforms a hardware data plane and vice versa. The final goal is to develop the unified queueing model with software and hardware switches. The unified queueing model will act as an analytical tool for engineers to the predict delay, packet loss and throughput in their SDN deployments. This goal has two main objectives, (i) to develop queueing models for a hardware-based SDN switches, and (ii) to compare queueing models for a software-based and hardware-based SDN switch.

### 1.4 Contributions

This thesis contributes to the analytical modelling of an SDN paradigm in the context of performance analysis for an SDN switch. The contributions are listed as follows.

Shared buffer vs. Priority queueing buffer. Queueing models for the shared buffer model and the priority queueing buffer model for an SDN switch were compared. Based on the comparative analysis, the priority queueing model has been shown to provide shorter delay while installing flow table entries in the switch. However, this benefit comes at the cost of a higher buffer capacity required for the priority buffer than the shared buffer model. Adopting a priority queue for an SDN switch provides better isolation between the data and control traffic.

- Internal Buffering. The queueing model for an SDN switch with an internal buffer was developed to investigate the potential benefits and trade-off of internal buffering in SDN switches. From the comparative analysis with an SDN switch without an internal buffer, it was observed that a switch with an internal buffer reduced the average delay and packet loss at the cost of extra switch buffer capacity required. Therefore, the internal buffering in an SDN switch significantly reduces the average delay and loss probability at the time of contention.

- Software vs. Hardware switch. Unified queueing models with and without the internal buffer were developed to characterise the performance of SDN-based hardware and software switches. SDN-based hardware switches with and without the internal buffer have not been investigated much, especially from the analytical modelling aspect. Therefore, unified queueing models are useful tools for network analysts to get quick insights into both SDN-based software and hardware switches. These tools help network analysts to predict performance measures such as delay and loss probability in SDN-based software and hardware switches. Delay and loss probability are important metrics for delay and loss sensitive applications in computer networks.

9

### 1.5 Thesis Outline

The rest of this thesis is organized as follows.

**Chapter 2** provides the overview of an SDN paradigm with different aspects of packet processing in an SDN switch. The related works on performance analysis of an SDN switch using queueing theory are reviewed in this chapter.

Chapter 3 compares two commonly used buffer sharing models for an SDN switch. These are the shared buffer model and priority queueing buffer model. The comparison investigates trade-offs between these two buffer sharing mechanisms.

**Chapter 4** investigates the effect of internal buffering in an SDN switch. The queueing model for an SDN switch with internal buffer is developed and compared against the queueing model for an SDN switch without the internal buffer. The benefits and trade-offs of using the internal buffer in an SDN switch are identified.

**Chapter 5** investigates the effect of a hardware switching in an SDN switch. The queueing models for a hardware-based SDN switch with and without the internal buffer are developed. These models are compared against a software-based SDN switch to develop guidelines for the selection of a software data plane or a hardware data plane.

**Chapter 6** concludes this thesis with a summary of findings and suggestions for future work based on the outcomes.

# Chapter 2

# **Background and Related Work**

This thesis investigates the packet processing aspects of the switch in the Software-Defined Networking (SDN) to improve the overall performance of an SDN. This chapter starts with the brief overview of an SDN to provide information about its concept, architecture, and one of its popular protocol – OpenFlow. It is then followed by an explanation of an SDN switch's packet processing aspects that need to be analysed. This is followed by an explanation of existing approaches for performance analysis of an SDN. The pros and cons of existing approaches are then described. The reasons for selection of analytical tools, queueing theory, and Quasi-Birth-Death process are briefly discussed in existing approaches for performance analysis.

Next, previous works that are related to queueing models for SDN switches are reviewed in detail. Finally, this chapter is concluded with the summary of background and related works.

### 2.1 SDN: Overview

In a networked system, switches/routers have two basic components: the control plane and the data plane. The control plane performs control logic such as routing protocols, middlebox configuration while the data plane

11

forwards the traffic based on control logic. The control plane and data plane are coupled together, thus enabling each switch/router to participate in route making decisions and data forwarding.

However, this tight coupling is not flexible when the network size increases. The control logic coupled with the hardware and the use of low-level programming languages makes the system rigid and complex. Therefore it copes poorly with issues of scalability, reliability and security which are more pronounced as the network size increases. These issues in the traditional network hinder the performance of the system as the network traffic is increasing day by day.

In order to cope with these issues in the traditional network, a new network paradigm called as "Software-Defined Networking" (SDN) emerged. SDN has two defining characteristics: (a) it separates the control plane from the data plane, and (b) it logically centralizes the control plane to direct multiple data plane elements through a software program [22].

Figure 2.1 shows the comparison between traditional networking and SDN architectures. In an SDN architecture, the control plane is decoupled from the data plane whereas the control plane and data plane are coupled together in the traditional networking architecture [3].

Figure 2.1: Comparison between traditional networking architecture and SDN.

The decoupling of control plane from data plane simplifies the function of a switch/router to that of forwarding traffic. The decoupled control is logically centralized and is named as the controller. Therefore, an SDN is the concept in which a network can be controlled and managed through software, for this reason it is termed as Software-Defined Networking. A switch/router can be configured remotely and network resources can be virtualized through the software.

A typical SDN consists of three components: a network element, an SDN Controller, and an SDN Application as shown in Fig. 2.2 [23].

Figure 2.2: The components of a typical SDN.

- Network element: This is a forwarding device (switch or router) with a data plane only. A network element allows the controller to manage its functions via a southbound interface.

- SDN controller: This is a software entity that has network wide abstract and controls the network's basic functions like routing policy, middlebox configuration, etc.

- SDN application: This is the software program that directs the controller to perform the network's basic functions via a northbound

interface [24].

There are three basic types of interfaces in SDN architecture: Southbound interface, Northbound interface, and East-West interface.

- Southbound Interface: This is the interface between the network element, that is the SDN switch/router, and the controller. The SDN data plane can be programmed with this interface. Some protocols for the southbound interface are OpenFlow [25], ForCES [26], Border Gateway Protocol (BGP) [27], Network Configuration Protocol (NETCONF) [28], and Location Identifier Separation Protocol (LISP) [29]. OpenFlow, being a popular and widely used standard [3] is used for analysis in this thesis.

- Northbound Interface: This is the interface between the SDN controller and SDN application. With this interface, the SDN controller is directed to perform specific functions such as routing, firewall, and load balancer [30]. Some examples of the northbound interface are Floodlight Representational State Transfer (REST) API [31], Open-Stack REST API [32], and Vyatta Remote Access API [33].

- East-West Interface: This is the interface between SDN controllers. With this interface, SDN controllers interact with each other. Currently, there is no standard for the east-west interface but efforts have been made to standardize it with gateway protocols like BGP (Border Gateway Protocol) [27], SIP (Session Initiation Protocol) [34], SDNi [35], and East-West Bridge [36].

OpenFlow is the southbound interface standard protocol proposed by the Open Network Foundation (ONF) [37]. The ONF is a user-driven organization for developing and standardizing SDN. It defines communication between the control plane and data plane in SDN by allowing programmability through the flow table contained in a switch/router. In the OpenFlow architecture [25], the OpenFlow switch maintains one or more flow tables. Flow tables are linked together to form a pipeline, where each flow table has flow table entries (FTE) which contain a set of match fields. These match fields are matched against the incoming packet and a specified action is applied. Every flow table has a table-miss entry which is

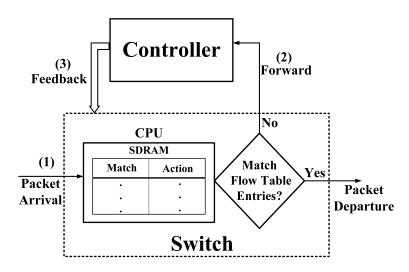

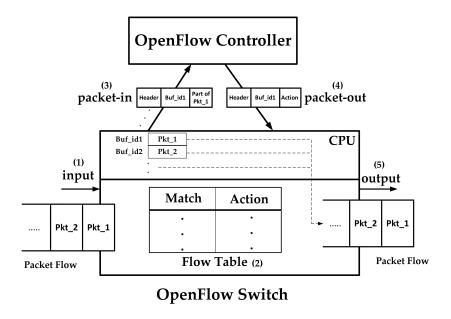

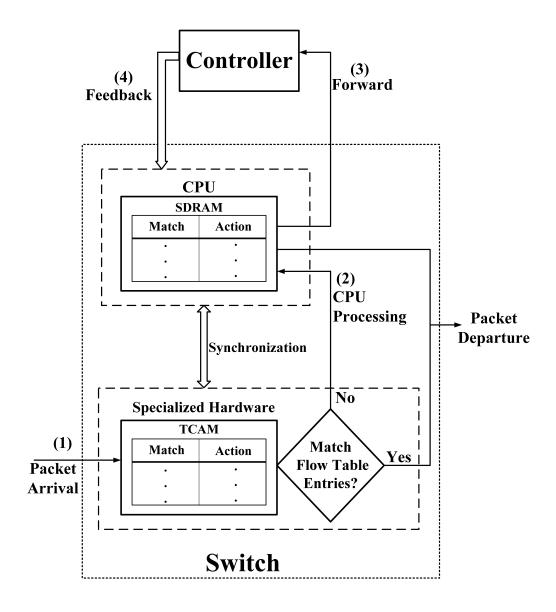

Figure 2.3: OpenFlow-based SDN architecture with one controller and one switch.

used if there is no matching flow table entry. This table-miss entry specifies what to do with an unmatched packet either by sending it to the controller, dropping it or directing it to next table. Figure 2.3 shows the OpenFlow-based SDN architecture with one controller and one switch.

### 2.2 Packet processing in an SDN switch

A computer communication network comprises of switches that forward packets from source to destination. The performance of any computer network largely depends on packet processing in a switch. For instance, faster processing switches can forward packets faster which reduces the overall delay in the network. Similarly, switches with sufficient memory can process a larger number of packets via internal buffering, thereby preventing loss of packets in the network. Therefore, it is important to analyse packet

processing aspects of a switch to obtain desirable QoS (Quality of Service) and improve the overall performance of a network.

SDN was introduced to simplify forwarding of packets. Switches in an SDN can be programmed through software that makes a computer network agile and flexible. SDN switches can be used in time-critical systems like industrial automation [19], interactive video [18], and online surgery [20] that require extremely low packet losses (i.e. below 10<sup>-4</sup>) [38]. However, design issues such as provisioning of switch capacity and buffer sharing mechanisms significantly impact the overall performance of an SDN. To address switch design issues and provide guidelines to network operators, various aspects of packet processing in an SDN switch have been analysed. These aspects include buffer sharing mechanisms, packet encapsulation methods, and SDN switch types which are discussed in the following subsections.

### 2.2.1 Buffer sharing mechanism

Decoupling the control and data plane presents a challenging opportunity for research in buffering requirements due to the different time scales of packet processing and traffic volume in the data plane and control plane. Packet processing in an SDN switch is categorized into: (i) fast path - referring to data plane processing (e.g. checksum calculation, TTL (time to live) decrement), and (ii) slow path - referring to the control plane processing, switch management functions, and exception processing (e.g. IP lookup). Packets traversing the fast path expect low latency, typically in orders of hundreds of nanosceconds while packets traversing the slow path experience tens of miliseconds delay.

Packet delays in a switch are determined by the capacity and service rate of the output buffers because output buffers in a switch are shared by all ports. Shared buffer switches are the most cost effective because multiple input ports share a single output buffer and reduces the cost and complexity of buffers to individual output ports in the switch. Alternatively, two separate buffers each serving the fast path and slow path can be used to buffer packets.

### 2.2.2 Packet encapsulation at an SDN switch

A packet encapsulation in the OpenFlow-based SDN is the encapsulation of an entire data packet or part of a data packet in the switch with an asynchronous message designated as "packet-in". A packet-in message is sent to the controller without a request from the controller when there is no matching flow table entries for an external data packet arriving in the switch [13]. Based on the configuration of a packet-in message, a packet encapsulation at an SDN switch can be categorized into three types:

- Full encapsulation of a packet (E): If an SDN switch does not support internal buffering due to insufficient memory, then full packet is encapsulated with a packet-in message. The full encapsulation method is the default packet processing used at an SDN switch.

- Internal buffering of a packet (I): If an SDN switch has sufficient

memory to buffer packets, then part of each buffered packet (i.e.

packet header that contains routing information which is used by

the controller to make forwarding decisions) along with an identifier

(i.e. buffer ID) is encapsulated with a packet-in message. In this case,

a packet to be internally buffered is temporarily queued at the switch

processor.

- Partial encapsulation of a packet (E-I): If an SDN switch with limited memory supports internal buffering, then packets will be queued at the switch processor until it has free available memory. When it runs out of memory to buffer packets, then a packet will be fully encapsulated with a packet-in message. Hence, this case is termed as the partial encapsulation of a packet.

In this thesis, "E" and "I" packet encapsulation methods are studied.

### 2.2.3 SDN switch types

SDN switches are categorized into Software-based Switch and Hardware or Physical Switch [4]. An SDN software switch maintains the flow table in SDRAM (synchronous dynamic random access memory) where the incoming packet is matched against the FTE using a CPU (central processing unit). If there is no matching FTE, a packet is forwarded to the controller which will feedback forwarding information to the switch and update the software flow table. The packet processing logic in a software switch is implemented in software [4] usually with the help of optimized software libraries. Open vSwitch (OVS) [39], Pantou/OpenWRT [40], of-softswitch13 [41], and Indigo [42] running on commodity hardware (e.g. desktops with several network interface cards) are a few examples of SDN software switches.

In an SDN hardware switch, the packet processing function is embedded in the specialized hardware. This specialized hardware includes layer two forwarding tables implemented using content-addressable memories (CAMs), layer three forwarding tables using ternary content-addressable memories (TCAMs) [4] and application-specific integrated circuits (ASICs). In a hardware switch, the FTEs are stored in CAMs and TCAMs of specialized hardware and packets are processed by the ASICs. Hardware switches are also equipped with SDRAM and CPU allowing a hardware switch to maintain flow tables in both TCAM and SDRAM [14]. Switches such as the Mellanox SN2000 series, NoviFlow NoviSwitch class of switches, HP ProCurve J9451A, Fulcrum Monaco Reference, Quanta LB4G, and Juniper Juno MX-Series are classified as hardware switches [43, 3].

In the following section, different approaches that are available for the performance analysis of an SDN network are discussed. The benefits and limitations of these approaches are briefly discussed followed by the reasons for the selection of analytical modelling.

### 2.3 Approaches for performance analysis

Computer communication networks are becoming complex and more advanced with the digital revolution. The technological advancement has changed different aspects of human life from education, research, development, and business [17]. Computer network designers are constantly working to improve the communication systems with the help of modelling and performance analysis tools. The performance analysis tool gives freedom and flexibility to network designers to study and predict a system before it's implementation.

As SDN is a new networking architecture, various design issues like traffic types (control and data traffic), switch buffer capacities, and buffer sharing mechanisms that can impact the overall performance of a network should be identified and analysed. For this purpose, we have to do performance analysis to identify the potential bottlenecks that can hinder the overall performance of an SDN network. The three commonly used performance measures for an SDN network are:

- Delay: This is the time that it takes to transmit a packet from a sender to a receiver.

- Throughput: This is the rate of a total number of packets transmitted to a receiver by a sender.

- Packet loss rate: This is the number of packets being blocked or dropped out of the total packets transmitted by a sender. It is expressed in a percentage.

In computer communication networks, these performance measures have a huge impact on the overall user experience. Delay and throughput determine the speed of the network while the packet loss rate is a negative indicator that causes a breakup in the communication.

The performance analysis of an SDN network has been done in three different ways: Experimental testbeds, Software-based tools, and Mathematical models [15]. From the survey shown in Fig. 2.4 that there are

not many mathematical models and experimental testbeds available for performance analysis of an SDN-based network. A hundred papers were surveyed which focused on SDN using the following keywords in Google Scholar, ACM Digital Library, IEEE Xplore, and SpringerLink: experimental testbeds, simulation, emulation, measurement tools, analytical models, performance analysis.

Figure 2.4: Approaches for performance analysis in SDN

### 2.3.1 Experimental testbeds

Experimental testbeds are real-time hardware testbeds which allow the researchers to validate and test their algorithms and mechanisms. Some of the examples of experimental testbeds used for an SDN are GENI (Global Environment for Networking Innovations) in the USA [44]; AKARI [45], JGN-X (Japan Gigabit Network-X) [46], and RISE [47] in Japan; FEDER-ICA (Federated E-Infrastructure Dedicated to European Researchers Innovating in Computing Network Architectures) [48], OFELIA (OpenFlow in Europe: Linking Infrastructure and Applications) [49], FIBRE (Future Internet Research and Experimentation) [46], and OpenLab [50] in Europe;

OF@TEIN [51] in South Korea and JOLNET [50] in Italy.

Experimental testbeds provide a flexible environment for testing, measuring, and validating new networking technologies and applications with real traffic. They can also use artificial traffic with packet manipulation tools like Scapy [52]. Experimental testbeds use high-performance real devices which make them more convincing than emulators and simulators [50]. However, experimental testbeds are expensive to deploy and have scalability problems due to hardware limitations [2, 50, 53, 54].

#### 2.3.2 Software-based tools

Software-based tools are used to debug, verify and simulate or emulate SDN applications and APIs [55]. Debugging and testing tools ensure the quality of an SDN software by getting rid of bugs and errors [56]. Some of the available debugging and testing tools are FlowChecker, ndb, Veriflow, OFRewind, OFf, OFTest, NICE, NetSight, PathletTracer, and SDN traceroute [2, 56]. Similarly, verification tools are used to verify and analyse the characteristics of SDN switches and controllers. Some of the available verification tools for an SDN are Cbench, OFCBenchmark, OFLOPS, OFLOPS-Turbo, OpenSketch, SDLoad [2].

A simulator is software that sets up a necessary environment to simulate the hardware's behaviour, while an emulator emulates every aspect of hardware's behaviour to make it an exact replica of actual hardware. Some examples of the simulator used in an SDN are NS-3, FS-SDN, MaxiNet, STS,VND-SDN, EstiNet 8.0 OpenFlow netowrk simulator, and OM-Net++ [2]. Mininet, Mininet CE, Mininet-HiFi and DOT[2] are examples of emulator. Simulators and emulators are low-cost and flexible compared to experimental testbeds. However, simulators use artificial traffic while emulators use real traffic [2, 3, 55, 56].

#### 2.3.3 Mathematical models

For the networks to be designed or operational networks that need to be optimized, a mathematical-based performance analysis is the cost-effective solution to predict performance measures [16]. The mathematical model represents the system in the form of mathematical equations, theorems and proofs. The model can be used to support experimental or simulated results. It also has the advantage of being cheaper and faster than the experimental framework or simulator. However, there are very few models available for mathematical analysis of an SDN-based network. The two basic mathematical methodologies used to model an SDN-based network are queueing theory and network calculus. The queueing theory shows the performance of a system in an average quantities at equilibrium state, while the Network Calculus shows the performance of a system in a probabilistic bound curve with the worst case scenario.

#### 2.3.3.1 Network Calculus

An SDN-based network has two level of services: flow-level and packet-level. A flow-level service is for the SDN-controller while a packet-level service is for an SDN switch [57]. The network calculus is used in an SDN for performance analysis of a flow-level arrival process which may consist of multiple or many packet-level arrival processes.

Network Calculus uses min-plus algebra and max-plus algebra to transform complex network systems into an analytical system that can be tractable [58]. Network Calculus is used for modelling a flow as a cumulative arrival process A. A(t) represents the total number of packet arrivals in the interval [0,t) [59].

The cumulative arrival process A at time "t" from any time "s" is characterized by the average sustainable arrival rate ( $\rho$ ) and the burstiness ( $\sigma$ ) such that  $A \sim (\sigma, \rho)$ :

$$A(t) - A(s) < \sigma + \rho(t - s), \quad 0 < s < t.$$

(2.1)

If constrained flows are merged, the resulting process is also constrained according to the multiplexing rule:

$$A_i \sim (\sigma_i, \rho_i) \to \sum A_i \sim (\sum \sigma_i, \sum \rho_i).$$

(2.2)

At time  $\tau$ , the stopped sequence ( $A^{\tau}$ ) is defined for increasing sequence A.

$$A^{\tau}(t) = \begin{cases} A(t), & \text{if } t \leq \tau, \\ A(\tau), & \text{otherwise.} \end{cases}$$

(2.3)

If there are no packet arrivals after time  $\tau$ , the stopped sequence  $A^{\tau}$  is equal to  $(\sigma(t), \rho)$  where

$$\sigma(t) = \max_{0 \le t \le \tau} \max_{0 \le s \le t} [A(t) - A(s) - \rho(t - s)]. \tag{2.4}$$

The summary of analytical models that use Network Calculus to model an SDN network is shown in Table 2.1. The analytical model presented in [60] has used network calculus to characterize the behaviour of the control interface with a single controller and switch. However, this model does not consider the interaction between the switch and controller. The interaction between switch and controller was considered in [57] with feedback model that computes worst-case bounds on performance metrics. The work in [57] was extended in [61] for scalable SDNs with multiple controllers. Similarly, [62] proposed the closed form expression to compute the worst-case bounds for the distributed control plane. The work in [63] proposed a hybrid scheduling model that combines PGPS (Packet Generalized Processor Sharing) and preemptive priority scheduling algorithms for multimedia flows in switches.

In the above-mentioned analytical models, a flow-level arrival in the controller and a packet-level arrival in the switch has been considered. However, for an SDN network where we want to study and analyse an SDN switch, queueing theory is a more useful mathematical tool to perform a packet-level analysis.

Table 2.1: Related works on SDN modelling using Network Calculus.

| Model                   | Contribution                               |  |  |  |  |

|-------------------------|--------------------------------------------|--|--|--|--|

| Bozakov, 2013 [60]      | Model to characterize the service of the   |  |  |  |  |

|                         | switch's control interface.                |  |  |  |  |

| Azodolmolky, 2013 [57]  | Feedback model to characterize interaction |  |  |  |  |

|                         | between the switch and controller.         |  |  |  |  |

| Azodolmolky, 2013 [61]  | Worst delay bound case for Scalable SDNs.  |  |  |  |  |

| Koohanestani, 2017 [62] | Delay bound based on the similarities be-  |  |  |  |  |

|                         | tween caches and flow tables in switches.  |  |  |  |  |

| Huang, 2017 [63]        | Hybrid scheduling model for multimedia     |  |  |  |  |

|                         | flows in switches.                         |  |  |  |  |

#### 2.3.3.2 Queueing theory

Queueing theory is the classical mathematical tool to study queues. It has been used for performance analysis and modelling of computer networks for many years where a computer network is represented as a network of queues [64]. It is used to analyse a network's delay and throughput at the steady state. In queueing theory, Kendall notation i.e A/S/c/K/D [65] is used to describe and classify a queue where

- A denotes inter-arrival time distribution,

- S denotes service time distribution,

- c denotes the total number of servers in the system,

- K denotes the maximum number of packets in the system, and

- *D* denotes the queue discipline.

The distribution of A and S may be Exponential Distribution (M), Deterministic Distribution (D), Erlang Distribution  $(E_k)$ , General Distribution (G), or Phase-type Distribution (PH), to name a few. Similarly, the common queue disciplines are FIFO (First In First Out), LIFO (Last In First

Out), SIRO (Service In Random Order), PNPN (Priority Service) and PS (Processor Sharing).

M/M/1 is the simplest queueing model where the system has one server with the arrival of Poisson distribution, service of exponential time distribution, infinite capacity and FIFO as default queue principle. The basic performance metrics determined using queueing theory in a computer network are delay and throughput.

The summary of analytical models that uses Queueing theory to analyse an SDN network is shown in Table 2.2. The model in [66] is the first analytical model for an SDN network with single switch and controller where switch (as M/M/1 queue) and controller (as M/M/1/K queue) are assumed to be operating independently. This assumption of independent operation was removed in [67] with the switch and controller collectively modelled as a Jackson's network. The work in [67] was extended in [68] with multiple switches. The model in [69] have modelled SDN-based cloud computing as a two-stage tandem network where the switch is modelled as M/M/1 queue with no distinction between the control and data traffic.

The models in [12] and [11] are the first to use priority buffer sharing models in the switch. The model in [12] uses a preemptive priority buffer while the model in [11] uses non-preemptive priority buffer in the switch. In both of these models, priority is given to the control packet over the data packet. However, the use of non-preemptive priority shows the accurate representation of an SDN behaviour where a packet in the processor is serviced without interruption. The work in [12] was extended in [70] with arrival assumed as an MMPP under bursty multimedia traffic scenario. Similarly, [71] have followed the work in [11] and have compared shared buffer with non-preemptive priority buffer sharing model in the switch. In [71], with the help of buffer dimensioning, they have shown that the use of priority buffer requires lower time to install FTE compared to a shared buffer model.

The model presented in [72] has assumed the switch service time distribution as a two-phase hyperexponential distribution and modelled switch as  $M/H_2/1$  queue which has been studied earlier in [73]. Similarly, the model presented in [74] also have assumed switch as  $M/H_2/1$  queue and proposed a network visualization and performance evaluation model based on [73] and [75]. In [72] and [74], two different service distributions for packets arriving at the switch are assumed. One of the service distributions is used to forward packets with matching flow updates, while the other one is used to send packets without matching flow updates to the controller. The use of two different service distributions paves the way for modelling hardware switches, one for the CPU and the other one for the TCAM.

The model presented in [76] have assumed the switch as M/G/1 model with log-normal mixture model as the service distribution. The work in [76] further demonstrates M/M/1 as a poor fit for the switch through experiments. The model presented in [77] is the first to model SDN hardware switch but does not consider a hardware data plane. In [77], the switch is assumed as M/Geo/1 model where inter-arrival is exponentially distributed and the service time is geometrically distributed.

The model presented in [78] models TCP connections over an SDN where both the switch and controller are modelled as MMPP/M/1. In [78], four-dimensional states are used to evaluate the performance of the switch and controller jointly under steady states, hence the model is named as the 4D state model.

The models presented in [79] are the first to model an SDN with NFV (Network function virtualization). In this work, two models: NFV under the controller, and NFV aside the controller are analysed. The comparative analysis in [79] shows that NFV aside the controller is a better architecture for integrating an SDN with NFV. The model presented in [80] is the exception that does not consider the switch and focused only on interactions between controllers.

Table 2.2: Related works on SDN modelling using Queueing Theory.

| Model               | Switch              | Contribution                                        |

|---------------------|---------------------|-----------------------------------------------------|

| Jarschel, 2011 [66] | M/M/1               | First to model an SDN where the switch and con-     |

|                     |                     | troller operate independently.                      |

| Mahmood, 2014 [67]  | M/M/1               | The switch and controller are collectively mod-     |

|                     |                     | elled as Jackson's network.                         |

| Yen, 2014 [69]      | M/M/1               | SDN-based cloud computing as a two-stage tan-       |

|                     |                     | dem network.                                        |

| Mahmood, 2015 [68]  | M/M/1               | Extension of [67] with multiple switches.           |

| Wang, 2015 [80]     | _                   | Only focuses on controllers, root and local con-    |

|                     |                     | trollers.                                           |

| Miao, 2015 [12]     | M/M/1               | Compare shared and preemptive priority buffer       |

|                     |                     | sharing models in the switch.                       |

| Shang, 2016 [72]    | $M/H_2/1$           | Two different service distributions for packets ar- |

|                     |                     | riving at the switch.                               |

| Xiong, 2016 [73]    | $M^X/M/1$           | Investigated the arrival flow request messages at   |

|                     |                     | the controller.                                     |

| Miao, 2016 [70]     | MMAP                | Extension of [12] with arrival as MMAP under        |

|                     |                     | bursty multimedia traffic scenario.                 |

| Sood, 2016 [77]     | M/Geo/1             | Among the first to model an SDN hardware            |

|                     |                     | switch.                                             |

| Goto, 2016 [11]     | GI/M/1/K            | Non-preemptive priority buffer model in the         |

|                     |                     | switch.                                             |

| Javed, 2017 [76]    | M/G/1               | Switch as $M/G/1$ with log-normal mixture model     |

| )                   | 3.5.47744           | as the service distribution.                        |

| Muhizi, 2017 [74]   | $M/H_2/1$           | Network visualization and performance evalua-       |

| 0                   | 07/27/2/75          | tion model.                                         |

| Singh, 2017 [71]    | GI/M/1/K            | Compare shared and non-preemptive priority          |

|                     |                     | buffer sharing models in the switch with buffer di- |

| 1 . 0045 [50]       | 1 (1 (DD /1 / / / / | mensioning.                                         |

| Lai, 2017 [78]      | MMPP/M/1            | TCP connection over an SDN.                         |

| Fahmin, 2018 [79]   | M/M/1               | An SDN with NFV.                                    |

In this thesis, we use queueing theory over Network Calculus to analyse an SDN switch. This is because the Network Calculus analyses worst case conditions of network which may result in over-provisioning of resources in real world production [62]. In queueing theory, the Quasi-Birth-Death (QBD) process has been widely used to model a computer network in greater detail [16]. Some examples that use QBD for detailed study of a computer network are scheduling of resource reservation [81], reliability of a computer system [82], telecommunication model with impatient customers [83], and modelling of P2P file sharing systems [84]. To study an SDN switch in greater detail, the modelling approach in this thesis is based on QBD processes. Hence, the following section is devoted to describe the notation and concepts behind QBD processes.

#### 2.3.4 Quasi-Birth-Death process

A continuous-time Markov chain with multidimensional state spaces that can be partitioned into disjoint levels is a QBD process [85]. A continuoustime QBD process is a two-dimensional Markov chain represented as

$$\{(X_t, Y_t), t \ge 0\} \tag{2.5}$$

with the state space  $\mathbb{S} = \{(i, j) \in \{0, 1, ..., K\} \times \{0, 1, ..., L\}\}$  where i and j denote the level and phase variables of the process, respectively [86]. Similarly, K and L determine the queue capacities of level and phase variables respectively which can be finite or infinite. In an SDN network, the controller may be represented by a level variable and the switch by a phase variable.

In queueing network, QBD processes can be multi-dimensional with one level variable and multi-dimension phase variables based on the number of the nodes or queues in the network. For N queues, the state of the network can be represented by the vector  $n = (n_1, n_2, ..., n_N)$  where  $n_l$  is the number of packets in queue l. If queue 1 is the queue of interest for

analysis, then packets at queue 1 (i.e.  $n_1$ ) are represented by the level variable and packets at queues other than queue 1 are represented by phase variables as the vector  $r = (n_2, n_3, ..., n_N)$  [87].

In QBD processes, the transitions between the state are limited within the level or between two adjacent levels. If the transitions of QBD process are independent of level, then such type of QBD process is homogenous or level-independent. Similarly, if the transitions are dependent of level, then QBD process is nonhomogenous or level-dependent [88].

#### 2.3.4.1 Homogenous QBD process

Using standard QBD notation [89], the transition matrix for a homogenous or level-independent QBD process is given by an infinitesimal generator matrix (Q) with a repetitive tri-diagonal block structure as shown below:

$$Q = \begin{pmatrix} B_1 & A_0 & & & & \\ A_2 & A_1 & A_0 & & & & \\ & A_2 & A_1 & A_0 & & & \\ & & \ddots & \ddots & \ddots & \\ & & & A_2 & A_1 & A_0 \\ & & & & A_2 & A_1 \end{pmatrix}, \tag{2.6}$$

where  $A_0, A_1, A_2$ , and  $B_1$  are standard notations of block matrices used to represent phase variable distributions in homogeneous QBD processes. The matrices  $B_1$  and  $A_1$  represent the phase distributions for boundary condition (i.e. i=0) and non-boundary condition (i.e.  $i\neq 0$ ) respectively when level variable remain unchanged (i.e.  $i\to i$ ). Similarly,  $A_0$  and  $A_2$  represent the phase distributions when level variable increases (i.e.  $i\to i+1$ ) or decreases (i.e.  $i\to i-1$  for i>0) by 1, respectively. In an SDN network,  $A_1$  or  $B_1$ ,  $A_0$ , and  $A_2$  represent homogeneous state distribution of the switch when the number of packets in the controller remains unchanged, increases by 1, and decreases by 1, respectively.

With the help of Matrix Geometric/Analytic Method [87], the stationary probability distribution  $\pi$  of homogeneous QBD process can be computed that satisfies the system of equations  $\pi Q = 0$  and  $\pi e = 1$ , where "e" is the column vector of ones. The stationary probabilities are defined as:

$$\pi_{ij} := \lim_{t \to \infty} \mathbb{P}(X_t = i, Y_t = j), \tag{2.7}$$

where  $\pi_i = (\pi_{i0}, \pi_{i1}, ..., \pi_{iL})$ , for i = 0, 1, ..., K and  $\pi = (\pi_0, \pi_1, \pi_2, ...)$ . The stationary probabilities can be used to compute network performance such as throughput, delay, and packet loss rate.

The homogeneous QBD process is positive recurrent and markov chain is ergodic if

$$\pi_A A_0 e < \pi_A A_2 e, \tag{2.8}$$

where  $\pi_A$  is the stationary probability vector of the matrix A which equal the sum of matrices  $A_0, A_1$  and  $A_2$ . For ergodic markov chain, the system of equation  $\pi Q = 0$  is equivalent to second-order difference equations

$$\pi_0 B_1 + \pi_1 A_2 = 0, (2.9)$$

$$\pi_{i-1}A_0 + \pi_i A_1 + \pi_{i+1}A_2 = 0, \quad i > 1,$$

(2.10)

with  $\pi_i = \pi_{i-1}R$  for  $i \geq 2$ , where R is the rate matrix of QBD process with dimensions  $(L+1) \times (L+1)$  and is non-negative solution to the equation

$$A_0 + RA_1 + R^2 A_2 = 0. (2.11)$$

The matrix R can be computed using various iterative algorithms like Successive Substitution (SS) [89], Logarithmic Reduction (LR) [90], and Cyclic Reduction (CR) [91]. However, the LR method has been widely used in performance analysis of communication systems due to a faster quadratic convergence rate [16, 92].

The LR method computes matrix G instead of directly computing the rate matrix R. The matrix G represents the hitting probability distribution on states in a given level and has an intuitive stochastic interpretation for

ergodic QBD process [87]. Like matrix R, matrix G is also characterized as non-negative solution which is dual equation to Eq. 2.11,

$$A_2 + GA_1 + G^2 A_0 = 0. (2.12)$$

The computation of matrices G and R using the LR method is shown in Appendix A.

#### 2.3.4.2 Nonhomogenous QBD process

The nonhomogeneous QBD process has been widely used to model telecommunication systems with dynamic stochastic arrivals and holding times [93]. It has level-dependent transition rates and is given by infinitesimal generator matrix Q using standard notation with a repetitive block structure [89],

$$Q = \begin{pmatrix} A_1^{(0)} & A_0^{(0)} & & & & & \\ A_2^{(1)} & A_1^{(1)} & A_0^{(1)} & & & & & \\ & A_2^{(2)} & A_1^{(2)} & A_0^{(2)} & & & & \\ & & \ddots & \ddots & \ddots & & \\ & & & A_2^{(K-1)} & A_1^{(K-1)} & A_0^{(K-1)} & \\ & & & & & A_2^{(K)} & A_1^{(K)} \end{pmatrix}, \tag{2.13}$$

where  $A_0^{(i)}$ ,  $A_1^{(i)}$ , and  $A_2^{(i)}$  are non-negative sub-matrices for  $i \geq 0$ . The sub-matrices  $A_0^{(i)}$ ,  $A_1^{(i)}$ , and  $A_2^{(i)}$  represent the phase variable distributions when level variable increases by 1 (i.e.  $i \rightarrow i + 1$ ), remains unchanged (i.e.  $i \rightarrow i$ ), and decreases by 1 (i.e.  $i \rightarrow i - 1$  for i > 0), respectively.

Similar to homogeneous QBD, the system of equations  $\pi Q = 0$  for nonhomogeneous QBD process is equivalent to the second-order matrix difference equations

$$\pi_0 A_1^{(0)} + \pi_1 A_2^{(1)} = 0,$$

(2.14)

$$\pi_0 A_1^{(0)} + \pi_1 A_2^{(1)} = 0,$$

$$\pi_{i-1} A_0^{(i-1)} + \pi_i A_1^{(i)} + \pi_{i+1} A_2^{(i+1)} = 0, \text{ for } i = 1, 2, ..., K - 1,$$

$$\pi_{K-1} A_0^{(K-1)} + \pi_K A_1^{(K)} = 0,$$

(2.14)

$$(2.15)$$

$$\pi_{K-1}A_0^{(K-1)} + \pi_K A_1^{(K)} = 0, (2.16)$$

#### 2.4. RELATED WORKS ON QUEUEING MODELS FOR AN SDN SWITCH31

with first-order recurrence scheme i.e.  $\pi_{i+1} = \pi_i R_i$  for i = 0, 1, ..., K - 1. Substituting  $\pi_{i+1} = \pi_i R_i$  in Eqs. 2.14, 2.15, and 2.16 yields

$$\pi_0(A_1^{(0)} + R_0 A_2^{(1)}) = 0,$$

(2.17)

$$\pi_{i-1}(A_0^{(i-1)} + R_{i-1}A_1^{(i)} + R_iA_2^{(i+1)}) = 0$$

, for  $i = 1, 2, ..., K - 1$ , (2.18)

$$\pi_{K-1}(A_0^{(K-1)} + R_{K-1}A_1^{(K)}) = 0, (2.19)$$

Equations 2.17, 2.18, and 2.19 are the solution to stationary distribution probabilities for the nonhomogeneous QBD process which requires the rate matrix for the highest level ( $R_K$ ).

There are various methods to compute  $R_K$ , out of which the Bright-and-Taylor method [94] and the Matrix Continued Fraction Algorithm (MCF) [95] are widely used. The Bright-and-Taylor method is among the first to compute rate matrices for nonhomogeneous QBD by approximating  $R_K$ . This approximation of  $R_K$  requires larger memory for computation and storage of iteration matrices to satisfy specified tolerance (say  $10^{-10}$ ). This may result in overflow or underflow errors in a memory-constrained network [83]. As an alternative, MCF method is faster and more efficient which assumes  $R_K$  as a zero matrix instead of approximating it. The algorithm for the MCF method is shown in Appendix B.

# 2.4 Related works on queueing models for an SDN Switch