# An FPGA Based Hardware Accelerator for Remote Surveillance Cameras

by

Alexander John Petre Kane

A thesis submitted to Victoria University of Wellington in fulfilment of the requirements for the degree of Master of Engineering in Electronic and Computer Systems Engineering.

Victoria University of Wellington 2013

### Abstract

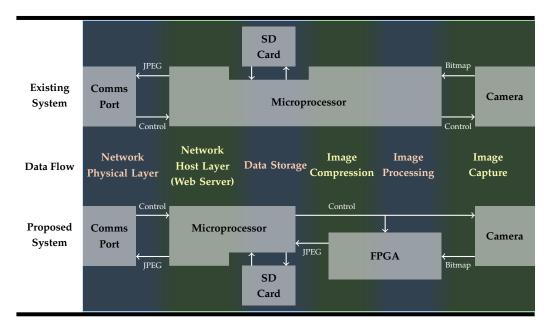

The Blackeye II camera, produced by Kinopta, is used for remote security, conservation and traffic flow surveillance. The camera uses an image sensor to acquire photographs which undergo image processing and JPEG encoding on a microprocessor. Although the microprocessor performs other tasks, it is the processing and encoding of images that limit the frame rate of the camera to 2 frames per second (fps). Clients have requested an increase to 12.5 fps while adding more image processing to each photograph. The current microprocessor-based system is unable to achieve this.

Custom digital logic systems perform well on processes that naturally form a pipeline, such as the Blackeye II image processing system. This project develops a digital logic system based on an FPGA to receive images from the image sensor, perform the required image processing operations, encode the images in JPEG format and send them on to the microprocessor. The objective is to implement a proof of concept device based upon the Blackeye II's existing hardware and an FPGA development board. It will implement the proposed pipeline including one example of an image processing operation.

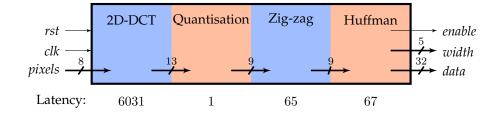

A JPEG encoder is designed to process the  $752 \times 480$  greyscale photographs from the image processor in real time. The JPEG encoder consists of four stages: discrete cosine transform (DCT), quantisation, zig-zag buffer and Huffman encoder. The DCT design is based upon the work of Woods et al. [1], which is improved on. An analysis of the relationship between precision and accuracy in the DCT and quantisation stages is used to minimise the system's resource requirements. The JPEG encoder is successfully tested in simulation.

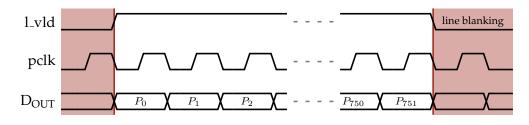

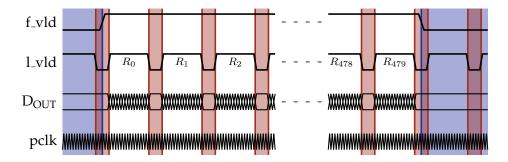

Input and output stages are added to the design. The input stage receives data from the image sensor and removes breaks in the data stream. The output stage must concatenate the data from the JPEG encoder and transmit it to the microprocessor via the microprocessor's ISI (image sensor interface) peripheral. An image sharpening filter is developed and inserted into the pipeline between the input and JPEG encoder. Because remote surveillance cameras are battery powered, the minimisation of power consumption is a key concern. To minimise power consumption a mechanism is introduced to track those modules in the pipeline that are in use at any time. Any not in use are paused by gating the module's clock source.

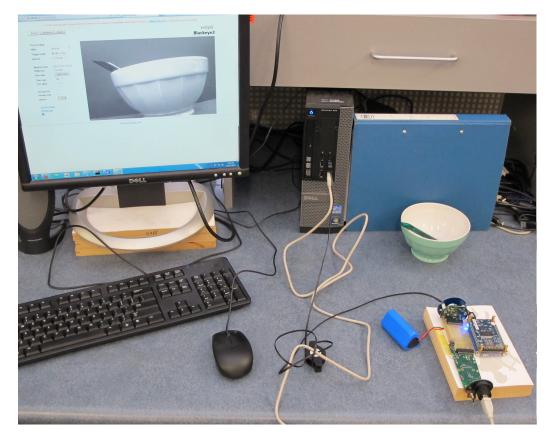

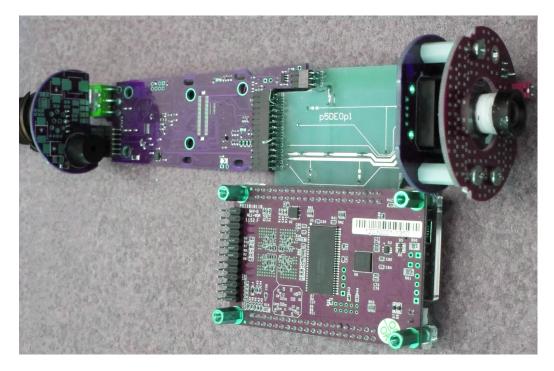

Once the system is complete and tested in simulation it is loaded into hardware. The FPGA development board is attached to the image sensor board and microprocessor board of the Blackeye II camera by a purposebuilt breakout board. Plugging the microprocessor board into a PC provides a live stream of images proving the successful operation of the FPGA system. The project objectives were exceeded by increasing the frame rate of the Blackeye II to 20 fps, which will not decrease with additional image processing operations.

The project was viewed as a success by Kinopta, who have committed to its further development.

# Acknowledgments

I am indebted to my supervisor, Prof. Dale Carnegie, for his support in this endeavour. He shared his wealth of experience in research and writing in guiding me to the completion of this thesis.

Much thanks is owed to Don Peat of Kinopta, without whom this project would not have been possible. He and Rick Hudson welcomed me into the team and provided financial, technical and moral support.

Victoria University Scholarships Office provided financial support when the initial funding of the project fell through.

This thesis would make for a poorer read if not for the many people who gave me feedback on it along the way. I especially would like to thank my mother, Jane Petre, who knows more about grammar than anyone else, Ann Hibbard and Dayna Kivell for telling me when my explanations were not up to scratch, Tina Rønhovde Tiller for her meticulous proofing, and Rory Sarten and my father, John Kane, for undertaking the Herculean task of reading the thesis from cover to cover in one go.

Thanks also go to all my friends and family for their support throughout, and for putting up with me hiding away in my writing cave and not coming out to play. iv

# Contents

| 1 Introduction |                           |                               |                                  |    |  |  |  |

|----------------|---------------------------|-------------------------------|----------------------------------|----|--|--|--|

|                | 1.1                       | Projec                        | t Goal                           | 4  |  |  |  |

|                | 1.2                       | Outlir                        | ne of Thesis                     | 4  |  |  |  |

| 2              | Bac                       | kgroun                        | d                                | 7  |  |  |  |

|                | 2.1                       | FPGA                          | s                                | 7  |  |  |  |

|                |                           | 2.1.1                         | FPGA Development Process         | 8  |  |  |  |

|                |                           | 2.1.2                         | CPU-FPGA coupling                | 12 |  |  |  |

|                |                           | 2.1.3                         | FPGA-based Hardware Accelerators | 14 |  |  |  |

|                |                           | 2.1.4                         | FPGA Design for Embedded Systems | 16 |  |  |  |

|                |                           | 2.1.5                         | FPGA Power Considerations        | 18 |  |  |  |

|                |                           | 2.1.6                         | FPGA Summary                     | 20 |  |  |  |

|                | 2.2 JPEG Algorithm        |                               |                                  |    |  |  |  |

|                |                           | 2.2.1                         | JPEG Modes                       | 22 |  |  |  |

|                | Discrete Cosine Transform | 24                            |                                  |    |  |  |  |

|                |                           | 2.2.3                         | Quantisation                     | 24 |  |  |  |

|                |                           | 2.2.4                         | Entropy Encoding                 | 26 |  |  |  |

|                |                           | 2.2.5                         | File Format                      | 29 |  |  |  |

|                |                           | 2.2.6                         | JPEG Summary                     | 29 |  |  |  |

|                | 2.3                       | 2.3 Image Processing on FPGAs |                                  |    |  |  |  |

|                |                           | 2.3.1                         | Image Processing Pipeline        | 31 |  |  |  |

|                |                           | 2.3.2                         | Image Processing Operations      | 32 |  |  |  |

|                |                           | 2.3.3                         | Summary of Image Processing      | 35 |  |  |  |

|                |                           |                               |                                  |    |  |  |  |

|   | 2.4  | Pre-existing FPGA-based JPEG Encoders                |   |  |  |  |  |  |

|---|------|------------------------------------------------------|---|--|--|--|--|--|

|   | 2.5  | Summary                                              |   |  |  |  |  |  |

| 3 | JPE  | Encoder Implementation 39                            | 9 |  |  |  |  |  |

|   | 3.1  | Discrete Cosine Transform                            | 0 |  |  |  |  |  |

|   |      | 3.1.1 1D-DCT Design                                  | 1 |  |  |  |  |  |

|   |      | 3.1.2 1D-DCT Implementation                          | 6 |  |  |  |  |  |

|   |      | 3.1.3 DCT Transpose Buffer                           | 1 |  |  |  |  |  |

|   |      | 3.1.4 2D-DCT Considerations                          | 3 |  |  |  |  |  |

|   |      | 3.1.5 Implementation and Testing                     | 6 |  |  |  |  |  |

|   | 3.2  | Quantisation                                         | 8 |  |  |  |  |  |

|   |      | 3.2.1 Quantisation Implementation and Testing 6      | 1 |  |  |  |  |  |

|   | 3.3  | Zig-Zag Buffer                                       | 3 |  |  |  |  |  |

|   | 3.4  | Huffman Encoder                                      | 3 |  |  |  |  |  |

|   |      | 3.4.1 AC and DC Encoder Modules                      | 7 |  |  |  |  |  |

|   |      | 3.4.2 Huffman Encoder Testing                        | 0 |  |  |  |  |  |

|   | 3.5  |                                                      |   |  |  |  |  |  |

|   | 3.6  | Overview of JPEG Encoder Implementation              |   |  |  |  |  |  |

| 4 | Syst | em Implementation 73                                 | 5 |  |  |  |  |  |

|   | 4.1  | Image Sensor                                         | 5 |  |  |  |  |  |

|   |      | 4.1.1 Image Sensor Interface                         | 7 |  |  |  |  |  |

|   |      | 4.1.2 FPGA ISI Module                                | 8 |  |  |  |  |  |

|   | 4.2  | Blackeye II Camera System                            |   |  |  |  |  |  |

|   | 4.3  | Microprocessor Interface                             |   |  |  |  |  |  |

|   |      | 4.3.1 Data Format                                    | 4 |  |  |  |  |  |

|   |      | 4.3.2 Output Module — Structure and State Machine 85 | 5 |  |  |  |  |  |

|   |      | 4.3.3 Output/Data Module                             | 8 |  |  |  |  |  |

|   | 4.4  | Power Reduction                                      | 1 |  |  |  |  |  |

|   | 4.5  | Image Processing Operations                          | 3 |  |  |  |  |  |

|   |      | 4.5.1 Image Sharpening Operation                     |   |  |  |  |  |  |

|   | 4.6  | System Summary                                       |   |  |  |  |  |  |

### CONTENTS

| 5 | Evaluation and Conclusion |                            |    |  |  |  |  |  |

|---|---------------------------|----------------------------|----|--|--|--|--|--|

|   | 5.1                       | The System in Operation    | 99 |  |  |  |  |  |

|   | 5.2                       | Comparison of JPEG Encoder | 01 |  |  |  |  |  |

|   | 5.3                       | Evaluation of System       | 06 |  |  |  |  |  |

|   | 5.4                       | Future Work                | 08 |  |  |  |  |  |

|   |                           | 5.4.1 Improvement          | 08 |  |  |  |  |  |

|   |                           | 5.4.2 Image Processing     | 10 |  |  |  |  |  |

|   |                           | 5.4.3 Configurability      | 11 |  |  |  |  |  |

|   | 5.5                       | Conclusion                 | 12 |  |  |  |  |  |

|   | 5.6                       | Statement from Kinopta     | 17 |  |  |  |  |  |

| A | JPEO                      | G Huffman Tables 1         | 27 |  |  |  |  |  |

| B | B JPEG Header             |                            |    |  |  |  |  |  |

|   | B.1                       | JFIF Header                | 36 |  |  |  |  |  |

|   | B.2                       | Tables                     | 37 |  |  |  |  |  |

|   | B.3                       | Frame Header               | 39 |  |  |  |  |  |

|   | B.4                       | Scan Header                | 39 |  |  |  |  |  |

|   |                           |                            |    |  |  |  |  |  |

vii

CONTENTS

viii

# Chapter 1

# Introduction

Remote surveillance cameras provide a means to observe places that are not easily accessible. For example, to monitor access points, farms that are vulnerable to trespassers require remote cameras that don't depend on the electric grid or fixed communication systems. The applications for such devices extend well beyond rural security. The conservation of native fauna is a major issue in New Zealand. Conservation workers are too stretched to watch out for every animal in their care, but using remote cameras allows them to observe the animals' behaviour, find out where they've been, or if pest species are in the area.

Kinopta is a small New Zealand company whose flagship product is the Blackeye II camera. This camera is designed to operate for days at a time on a single battery charge. It takes photographs regularly for the entire period of operation. When the batteries are low, the camera is accessed and the batteries changed or recharged. When it is accessed by a PC, either via USB or wirelessly, it presents itself as a website for the user to access, browse and download the photos.

A major strength of the Blackeye II as a remote surveillance camera is its unobtrusive night-time photography. It takes high quality photos in dark conditions without the use of any flash perceptible to human or animal. Most locations where remote surveillance cameras are used are devoid of artificial light, so many competing cameras struggle to perform at night. To increase battery life other camera systems stop taking and storing photographs if the scene remains unchanged, but these systems may miss events that happen quickly. For example, cameras are known to use passive infra-red sensors to trigger the camera. A kakapo leaving its nest will trigger the camera because it is warm, but when it returns its feathers will have cooled and it will not trigger the camera. The Blackeye II is in constant operation and will not miss events. However, this makes it even more important that it uses as little power as possible.

Kinopta treats the Blackeye II as a product platform; they customise the camera for different applications. Blackeye II cameras are currently used for the applications described above as well as traffic flow planning surveys. In each of these applications the Blackeye II was selected for its superior night time photography. The camera system is highly flexible and applications under development extend to medical instrumentation.

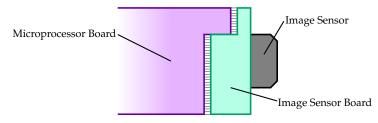

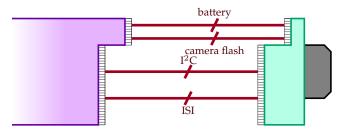

The two main components to the camera are the image sensor and microprocessor. The image sensor captures the digital images and sends them to the microprocessor. The microprocessor performs image processing operations on the images, encodes them as JPEG files and stores them on-board. The camera hosts a web server so that when it is networked with a computer the user can access it with a web browser. Using an embedded web server allows the camera to provide a custom interface for easy access to the images stored on-board without the need to install custom software on the PC.

Clients are demanding new and improved features on the cameras, but these are proving hard to fulfil with the current system. Faster frame rates are required for traffic monitoring where cars are not in shot for long. Conservation workers need to observe fast events, such as pest species preying on kiwi and other endangered NZ birds, so their cameras also require a faster frame rate. A frame rate of 12.5 fps (frames per second) has been identified as being sufficient for these applications. However, the current system is only capable of taking photos at 2 fps. The microprocessor in the camera must perform operations on every frame as it arrives and it is unable to keep up with a faster frame rate.

In addition to a faster capture rate, clients demand improved image quality. The nature of these improvements depends on the application. Traffic flow planning operations require the identification of individual cars travelling through a city, so require that the license plates on cars are clearly legible. Monitoring of wildlife reserves requires that a wide field of view is recorded. It should be able to detect creatures moving in the shadows in the background. These improvements in image quality can be achieved with image processing techniques, but as more image processing operations are added to the system, the frame rate decreases even further.

The microprocessor could be upgraded to a more powerful one, but this increases the cost and power consumption of the device and still presents a trade-off between frame rate and image processing capability. An alternative is to add a digital hardware system to the camera to perform the image processing and encoding. Digital hardware systems can be designed in a pipeline to eliminate the trade-off between data rate and the number of operations being performed.

This project proposes the use of a field programmable gate-array (FPGA) device to implement a digital hardware image processing system. FPGAs are highly flexible digital devices that allow for the implementation of almost any kind of digital logic. The proposed system will sit between the image sensor and microprocessor in the data flow. It will take the images from the image sensor, perform the necessary image processing operations on them, then encode them as JPEG data before sending them to the microprocessor for storage. It was decided to continue using JPEG encoding rather than other types of image encoding due to its compression levels and widespread use.

## 1.1 Project Goal

As mentioned, there is demand for greater features and faster performance of the Blackeye II camera. Its microprocessor is unable to provide these. It can achieve a frame rate of only 2 fps with the current image processing pipeline. The company, Kinopta, would like the Blackeye II camera to be able to capture photos at a rate of 12.5 fps with the addition of more image processing operations. The camera runs off battery for long periods, so the power consumption of the improvements must be kept low.

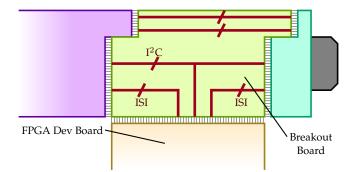

This project will develop an FPGA-based system to complement the microprocessor in the Blackeye II camera. The aim is to develop a system that will receive data from the image sensor, perform image processing on the data, encode it as a JPEG file and send it to the microprocessor. A proof-of-concept device will be constructed to show the system in operation. It is not the goal of this project to take the system through to a production-ready prototype. Instead the design will consist of an architecture for an image processing pipeline, an example image processing operation to insert in that pipeline, a JPEG encoder and interfaces to the image sensor and microprocessor. Throughout the design process care will be taken to minimise the power consumption of the device.

## **1.2** Outline of Thesis

This thesis continues in Chapter 2 by covering relevant background knowledge. This includes FPGA use in industry, their advantages compared with other devices, and how FPGAs can be included into systems. An overview of JPEG encoding is provided along with detail of important parts. Chapter 3 sets out the design process of the JPEG encoder. Previous work in the field is used and improved. Particular care is taken to explore the trade-off between precision and accuracy in the design in order to minimise the design resources. Chapter 4 discusses the interfaces between

#### 1.2. OUTLINE OF THESIS

FPGA and image sensor, and FPGA and microprocessor, and the design of the parts of the system responsible. A power saving mechanism is introduced and implemented, as well as an image sharpening filter. Chapter 5 begins by discussing the final implementation of the system and its performance. It then evaluates the system with regard to the project objectives, and the JPEG encoder is compared with other implementations. Finally, a discussion titled *Future Work* provides a path forward from this project to a final product.

# Chapter 2

# Background

## 2.1 FPGAs

An FPGA is a reconfigurable digital logic device. FPGAs have a configurable interconnect network linking from  $10^3$  to  $10^6$  logic elements. A logic element (LE) usually consists of some type of configurable look-up-table (LUT), a flip-flop and a multiplexer. By configuring the LEs and the interconnects, an FPGA can behave as almost any digital logic system provided it has sufficient resources.

FPGAs may be used in the same roles as fully customised integrated chips such as ASICs (Application Specific Integrated Chip). ASICs, unlike FPGAs, are not reconfigurable, which does have advantages. There are extra resources devoted to reconfigurability and the layout of the active resources in a reconfigurable system is sub-optimal. This results in longer signal paths and extra logic gates to perform the same task. Therefore there are drawbacks to implementing the same design in an FPGA compared with an ASIC: clock paths aren't as efficient, and therefore the same clock rates aren't achievable; static and dynamic power efficiency is worse; and silicon wafer area efficiency is poorer, therefore FPGAs have a greater per unit cost.

The reduced per unit cost of ASICs means that for large volume pro-

duction they are preferred to FPGAs. However, the non-recurring engineering (NRE) cost of developing an ASIC is significantly higher. While the digital logic design is a part of the NRE of both FPGA and ASIC projects, the ASIC process requires the logic to then be organised into a transistor-based design and the appropriate wafer patterns produced. Not only do these additional stages add to the cost of each design iteration, they add significantly to the time between iterations. Reducing development iteration time and cost, allows for the development to proceed more smoothly; unexpected errors can be rapidly solved before moving on. Reconfigurability also means that systems may be upgraded after production. Due to these advantages FPGAs are used in projects where the volume of production isn't sufficient to warrant the use of ASICs. The volume at which this occurs is increasing over time because FPGAs are being more widely accepted in industry, they become more energy efficient and their per unit cost decreases [2].

FPGAs were developed by Xilinx in the 1980s and are now a major product market currently dominated by Xilinx and Altera, with other companies taking a niche role. As the feature set of FPGAs has increased, the development tools have matured and the per unit costs have reduced, FP-GAs are becoming increasingly common in product design in every sector of electronics. In addition to LEs and the interconnect network, modern FPGAs also have specialised hardware blocks, which commonly include RAM, multipliers, Phase Locked Loops (PLLs), and highly configurable I/O blocks for each individual I/O pin [3].

#### 2.1.1 FPGA Development Process

While there are a range of independent development tools for FPGAs, development commonly utilises the toolchain produced or supported by the manufacturer of the target FPGA. This project uses an Altera FPGA from the Cyclone IV range.

#### 2.1. FPGAS

Altera provides the Quartus II development software for FPGAs in both free and paid versions. The free version was used here because none of the restrictions of the free version inhibited the project. Quartus II provides several environments to edit functional designs, including the use of hardware description languages (HDLs). This software provides all the toolchains required to turn a design into a *programming file*. It is then able to load the programming file onto an FPGA board connected to the computer. Quartus II provides a wide range of tools to customise and optimise the system beyond just the functional design. Alongside Quartus II, Altera recommends the use of its own customised version of Mentor Graphic's ModelSim software for simulation of HDL designs. Functional design of this project is written in a language called Very-High-Speed Integrated Circuits (VHSIC) HDL, shortened to VHDL. Quartus II is used to synthesise and ModelSim to simulate this design. The following discussion on the development process is specific to these design tools.

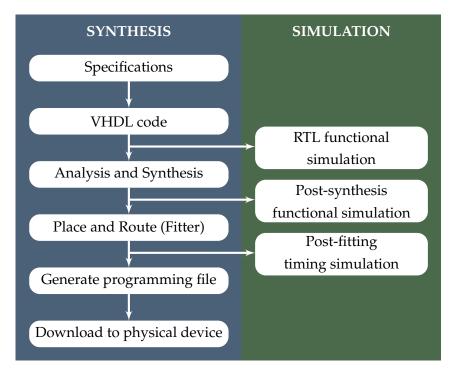

A simplified VHDL-based FPGA design flow is depicted in Figure 2.1 as suggested by Pedroni [4]. The process begins with a specification stage, often utilising block diagrams, state machine diagrams and other hardware design techniques. The design is then turned into VHDL code.

VHDL specifies the functional operation of the system, and is primarily based on the concept of signals. Signals in VHDL are strongly typed buses within the system of specified width. While strong typing is employed, the language does allow for significant flexibility; signals can undergo type conversion, so that a signal of type *standard logic vector* (an ordered 1D array of bits) can become the input to a signal of type *unsigned integer*. Signals may undergo a wide range of concurrent and sequential operations from a set of standard libraries (with the option to use user-defined libraries as well). An unsigned integer, for example, has arithmetic operations, such as addition and multiplication, available from a standard library. The code is organised by blocks called *entities*, which may consist of logical operations and other sub-entities known as *components*. An

Figure 2.1: FPGA design flow.

entity can be thought of as corresponding to a block in a hardware block diagram and is referred to in this document by the generic term *module*. A module is defined by its I/O interface and its constituent logic.

The next stage of FPGA development is the analysis and synthesis of the VHDL code. This is performed by the development environment, in this case Quartus II, and the development environment will offer different ways to optimise or otherwise influence the analysis and synthesis process. This process converts the HDL description of a system into a netlist of hardware blocks and interconnecting buses. The hardware blocks of these netlists do not represent FPGA hardware components, but are abstract elements that are readily translatable into FPGA hardware components. Note that some signals and operations that are part of the VHDL code will not be explicit in the netlist, but will instead be combined with other signals and operations or removed entirely as part of the optimisa-

#### 2.1. FPGAS

tion process. Where signals do explicitly correspond to VHDL signals, the VHDL labels are retained.

Following this stage, is the place and route process, also known as the *fitter*. This, again performed by development software, converts the functional netlist into a description of the utilisation of specific hardware components of the target device. This process is also used to ensure timing limitations of the system. Due to the complexity of FPGA hardware, signals that pass through several hardware resources can experience significant propagation delays. By specifying the timing requirements of a system, the fitter will attempt to ensure these are fulfilled.

In order to use the design on an FPGA, its configuration must somehow be sent to the FPGA. FPGAs use different communication standards to receive configuration data, which is determined by the manufacturer. The programming file specifies how the FPGA should configure its interconnect network, LUTs and other hardware components. Once generated, FPGA programming software is used to transmit the program file to the FPGA via some on-board communication system.

Alongside the synthesis is the simulation process. If a VHDL system passes rigorous simulation tests it is almost guaranteed to pass physical testing [4]. As indicated by Figure 2.1, there are three levels of simulation. All reference to simulation from here on refers to functional simulation. Timing simulation involves calculating propagation delays and displaying their effects. However, timing simulations were not necessary in this project because at no point was the logic sufficiently complex to cause propagation delays comparable with the clock speeds.

A VHDL simulation requires a special type of VHDL module called a *testbench*. A testbench instantiates the module to be tested and specifies the generation of the module's input signals. Signals in a testbench may be read from or written to files. Simulations can be set up to launch from Quartus II, which will run ModelSim and provide it with an automatically generated script to run. While testbenches may output information to a command line, a simulation is primarily viewed via a timing diagram interface. In functional simulations the timing diagram assumes zero propagation delays so concurrent operations will occur concurrently, and sequential operations will occur on clock edges. The user may view any signal of the testbench, the main module or any of its constituent modules (so long as that signal still exists post-synthesis). Many signals may be selected simultaneously, and the waveforms of these signals are generated for a user specified simulation period. The timing diagram allows the developer to view the entire operation of a system in great detail in order to track down system bugs.

#### 2.1.2 CPU-FPGA coupling

Advanced embedded systems are traditionally software driven; they are controlled by a CPU. While FPGAs provide improvements in many processing applications, many tasks are much better suited to software. As FPGAs have become increasingly common in these systems the various configurations by which they are coupled to the system's CPU have been categorised [5, 6]:

The most closely coupled case is that of a CPU with reconfigurable hardware functions integrated into it. The purpose of such a close coupling is to allow the reconfigurable hardware to add to the core architecture of the CPU. Custom instructions can be implemented to accelerate particular algorithms, passing data via shared registers. Closely linked to this is the increasingly common phenomenon of soft CPU cores, that is, CPUs that are implemented on an FPGA. These CPUs are becoming increasingly mature, particularly those provided by the major FPGA manufacturers such as Altera's NIOS II and Xilinx's MicroBlaze. These allow for a highly customisable CPU system with optional instructions easily added or removed.

#### 2.1. FPGAS

- 2. The next most closely coupled case is a coprocessor system. The reconfigurable hardware has more independence than the functional unit described in 1, while still being highly integrated into the CPU. The coprocessor may receive a trigger from the CPU and operate independently for several clock cycles until a result is achieved. A clear advantage to this system is the core CPU and reconfigurable hardware may operate in parallel, which provides performance gains at the cost of added care required in software design. The coprocessor has access to the CPU's memory cache, as opposed to direct access to CPU registers as in 1.

- 3. An attached processing unit is one stage further from the CPU. It is further removed in terms of memory access too: it does have access to the CPU's memory, which it shares control of via a direct memory access (DMA) system. Communication between the CPU and the attached processing unit is therefore slower than the above cases, although direct memory access does allow for such a processor to undertake large tasks on data independently from the CPU and return the result in place for the CPU to easily access it.

- 4. A standalone system is one where the CPU and reconfigurable hardware are not integrated. The reconfigurable hardware will operate largely independently of the CPU and only infrequently communicate with it via system I/Os or a network link. This is the case where an FPGA and CPU are both part of a single device but do not share memory.

In general, reconfigurable hardware more closely integrated into the CPU has greater and faster access to it, but is more dependent upon it. Furthermore, the more highly integrated system will generally have fewer reconfigurable hardware resources than independent systems. Garcia et al. [7] propose a similar categorisation but with three categories: a functional unit (as in point 1 above); a coprocessor, which has access to the

CPU's memory and possibly its cache (as in points 2 and 3 above); and a heterogeneous multiprocessor, which may have a shared memory system or may communicate via a network or communication architecture (as in 3 and 4 above). The latter categorisation more closely reflects the necessary physical integration levels between reconfigurable hardware and a CPU: amalgamated into the CPU architecture, as a peripheral of the CPU, or on an independent chip. A general term for the reconfigurable hardware in these systems is a hardware accelerator, though this term also applies to other hardware systems.

### 2.1.3 FPGA-based Hardware Accelerators

FPGAs provide a hardware solution to many engineering problems. Software solutions running on a microcontroller or microprocessor can provide equivalent results. Each design task has its own problems that need to be solved, and an appropriate selection of technology is required to provide an appropriate solution. Table 2.1 provides a list of general advantages of software over hardware and vice versa.

Table 2.1: List of advantages of software and hardware in the general case.

| Software                   | Hardware                  |

|----------------------------|---------------------------|

| Rapid updates              | Highly optimised system   |

| Lower development time     | Faster system performance |

| Expertise widely available | More power economical     |

| Lower development cost     |                           |

The choice between using software or hardware goes beyond that of resource cost versus degree of system optimisation. The degree to which systems can be improved through the use of hardware, or the reduction in development time for software, depends entirely upon the task being undertaken. While research is being done on the potential for systems

#### 2.1. FPGAS

to be accelerated by FPGAs, the advantages of software have previously inhibited widespread uptake of FPGAs in industry [8].

CPUs excel at performing linear tasks where a lot of decision making occurs, and software systems are highly adaptable. Hardware systems are inherently less flexible and therefore are largely confined to tasks that are well defined. On the other hand hardware can perform operations on an almost limitless level of parallelism, whereas CPUs only perform one operation at a time, so are not suited to tasks that are well pipelined.

Digital system design faces continuous performance pressures. These pressures may be relieved by the appropriate use of hardware. This relief is needed, but at the same time so is the flexibility and rapid development cycles of software. To this end, there is an increasing use of digital hardware solutions coupled to software systems. Hardware accelerators are specialised hardware systems that are used to augment a software system, providing the benefits of a hardware solution to those parts of the system that stand to gain the most from it.

Specifically, the gains may be either in data throughput or in power reduction, or both. As mentioned at the start of Section 2.1, FPGAs do not provide the same gains in power reduction, nor are they capable of running at the same clock speeds as ASICs, but despite this they are capable of outperforming a microprocessor for some tasks. However FPGAs have made great progress in these areas in recent years [9].

The performance of hardware accelerators is measured by two metrics: run time and power consumption. Run time specifies how long it takes to perform a given operation, usually its main function, which may be compared with the equivalent run time in software. The power metric is defined as the average power consumption during the run time. The product of the power consumption and the run time is the operation energy. Again a direct comparison with software may be made. The overall power savings are more complex because the static energy (that is the energy consumed when the operation is not being performed) of the accelerator must be taken into account as well as the proportion of time the accelerator is operating. Furthermore, no net power savings of a system will be achieved unless the energy consumption of the software system is decreased. Simply put, either the processor is clocked slower, enters a low power mode for longer periods of time, or is replaced by a lower power processor as a result of the addition of the hardware accelerator. Alternatively, rather than reducing power, the addition of the accelerator may be incorporated in order to increase the system throughput, in which case the total power consumption of the system may remain static, or in fact increase.

Traditionally FPGAs have been coupled to CPUs to provide what is known as *glue logic* [5], that is, an interface between one digital system, such as a CPU, and another digital system. The role of hardware accelerators has taken them into new fields where they have proved successful. These fields include networking, encryption, software-defined radio, medical imaging, scientific data acquisition and analysis, spacecraft, robotics, automotive and image and video [7].

#### 2.1.4 FPGA Design for Embedded Systems

Portable embedded systems are becoming increasingly ubiquitous. The demands on embedded systems increase in the form of greater performance and flexibility, lower power consumption, and cheaper costs [10]. The incorporation of an FPGA may reduce the requirements of the microprocessor, so that a lower power microprocessor solution might be used. While the addition of an FPGA will make a significant contribution to the static power consumption of a device, they enable vast reductions in the dynamic power consumption of algorithms. An algorithm may take many more clock cycles to perform on a CPU than in an FPGA, if it is sufficiently pipelinable.

To show the effects of parallelism, an example is provided based on

the pseudo-code example in Figure 2.2. This simple algorithm takes input array, E, performs operations  $OP_1$  and  $OP_2$  on the data then outputs the result to array E".

for  $i = 0 \rightarrow 9$  do  $E'[i] = OP_1(E[i])$ end for  $E''[0] = OP_2(E'[0], 0)$ for  $i = 1 \rightarrow 9$  do  $E''[i] = OP_2(E'[i], E'[i-1])$ end for

Figure 2.2: Example algorithm

Assuming both operations can be computed in a single step then a clock by clock comparison of how this algorithm would progress on a CPU and an FPGA is given in Table 2.2. Parallelism means that while the FPGA may take as many clock cycles as the CPU for each data element, the FPGA will output one result each clock cycle, whereas the CPU will output one result every four clock cycles.

**Table 2.2:** Comparison of the performance of an algorithm as implemented on CPU vs. FPGA.

| clk | CPU                     | FPGA           |             |                    |                  |  |  |

|-----|-------------------------|----------------|-------------|--------------------|------------------|--|--|

| 0   | fetch( $E_0$ )          | $fetch(E_0)$   |             |                    |                  |  |  |

| 1   | $E_0' = OP_1(E_0)$      | fetch( $E_1$ ) | $OP_1(E_0)$ |                    |                  |  |  |

| 2   | $E_0'' = OP_2(E_0', 0)$ | $fetch(E_2)$   | $OP_1(E_1)$ | $OP_2(E'_0,0)$     |                  |  |  |

| 3   | store( $E_0''$ )        | fetch( $E_3$ ) | $OP_1(E_2)$ | $OP_2(E_1', E_0')$ | store( $E_0''$ ) |  |  |

| 4   | fetch( $E_1$ )          | fetch( $E_4$ ) | $OP_1(E_3)$ | $OP_2(E'_2, E'_1)$ | store( $E_1''$ ) |  |  |

| 4   | $E_1' = OP_1(E_1)$      | fetch( $E_5$ ) | $OP_1(E_4)$ | $OP_2(E'_3, E'_2)$ | store( $E_2''$ ) |  |  |

| :   | :                       | :              | :           | :                  | ÷                |  |  |

The mechanism by which an FPGA may reduce power consumption springs from parallelism. As shown in the example above, an algorithm implemented in a parallel manner may be performed in far fewer clock cycles per data element. Therefore, to achieve the same data rate as the CPU, the FPGA must be clocked at a slower rate. As dynamic power consumption is directly proportional to clock rate, the power used by the FPGA for the algorithm is likely to be less than that off the CPU despite its inherently poorer power efficiency. Conversely, if the FPGA were to be clocked at a faster rate the overall power consumption may stay the same or even rise, but the data rate will be increased significantly. The benefits of using hardware accelerators can be significant, with examples showing a 90% power reduction for the same data rate, or a 200-fold data rate increase for the same power [11].

### 2.1.5 FPGA Power Considerations

The power usage of an FPGA differs across three time periods: power-up, configuration and execution. Note that Flash-based FPGAs, as opposed to the predominant SRAM-based chips, will be slightly different. Power-up refers to the spike in current draw during the initial few microseconds of power being provided. This is dependent upon the chip itself rather than its configuration, and is largely attributed to on-chip SRAM. Configuration occurs shortly after power-up, and at any point during operation in which the system is reconfigured. The execution component accounts for the rest of the FPGAs operation, and consists of both dynamic and static power [12].

Static power consumption is constant for a given device. The static power consumption of FPGA devices is a major point of competition between vendors, so that devices with equivalent resources are decreasing in static power from one generation to the next, and vary considerably between vendors [2]. Within a family of devices the tendency is for static

#### 2.1. FPGAS

power to be proportional to the resources on the device. Dynamic power is dependent upon the rate at which signals change value due to the nature of CMOS architectures. Significant dynamic power consumption occurs both in the LEs and the interconnect [12]. Different configurations of the same functional design has different power efficiencies (for example, minimising the number of gates that might change on every clock cycle reduces dynamic power consumption).

To attain the best possible results from a hardware accelerator, the power consumption of the FPGA must be carefully considered. FPGA development software have variants of their place and route algorithms that favour low power design over other design parameters. The system on the FPGA, or any constituent system thereof, may not be utilised 100% of the time, therefore clock-enable systems may significantly reduce the proportion of the time that large parts of the chip are clocked without any reduction in performance. Specialised clock trees in the recent FPGAs' interconnect have allowed hardware clock gates to be implemented which are a vast improvement over clock gating via LEs, and furthermore are easily implemented with the vendor-supplied development software [13]. Idling systems for microprocessors are less flexible by comparison; the CPU, being the point of processing, must be fully active whenever any processing is required.

A complementary approach to reducing the FPGAs power consumption is to minimise the resource usage of the design, which has two effects: it decreases the overall dynamic power usage by minimising the size of dynamic systems; and it enables the use of FPGAs with fewer resources, and therefore lower static power consumption.

Some vendors produce FPGAs for low-power systems. These lowpower FPGAs generally have fewer resources available than their standard counterparts. This provides further incentive to reduce the power resource usage of systems designed for FPGA. The proof of concept system built for this project uses an Altera Cyclone IV FPGA, which is not considered a low-power device. This FPGA was chosen for convenience in the development process. However, the design of system is kept as vendor neutral as possible so that it may be ported to a different FPGA range in the future once the final resource usage and power consumption has been considered.

#### 2.1.6 FPGA Summary

FPGAs present a compelling alternative to ASICs in digital hardware design, particularly for low volume production. The advantage of an FPGA system are the comparatively low development costs and rapid design iterations.

While they compete against CPUs in some applications, in a hardware accelerator configuration, FPGAs are used to complement the main processor of the digital system. The coupling between the processor and configurable logic may be very close, where the hardware extends the capabilities of the processor, or may be distant, where an FPGA operates on data independently only communicating where necessary with the CPU.

The Blackeye II camera system currently does all of its image processing and encoding on a microprocessor. This project proposes the use of an FPGA in between the camera sensor and microprocessor to offload these processes from the microprocessor (see Chapter 4). By careful design the additional hardware may improve the overall performance of the system.

This project uses a Cyclone IV FPGA from Altera, one of the two main FPGA manufacturers. Development is done in the hardware description language VHDL using Altera's Quartus II development software to synthesise designs and Mentor Graphic's ModelSim to simulate them. During the design process, care was taken to reduce the system's resource usage and power consumption.

## 2.2 JPEG Algorithm

The Joint Photographic Experts Group (JPEG) was formed in 1986 to establish a standard for the encoding of greyscale and colour images [14]. The resulting document published in 1992, officially titled *Information Technology–Digital Compression And Coding of Continuous-Tone Still Images– Requirements And Guidelines,* is commonly referred to by the name of the committee: JPEG. The standard itself is not a single algorithm, but provides a set of rules for the compression of images; however, the appendices elaborate on the standard by providing examples, which are commonly used for JPEG implementation. The standard does not specify a file format, but provides a structure to add file information. EXIF and JFIF are the two common file formats for JPEG images, and both are read by most software [15].

JPEG has become the most used format in digital image storage [16]. In the case of digital photography JPEG has become the de facto standard. The advantage of JPEG use in photography is that, of the common image formats, it provides the greatest level of compression [17] by exploiting the following. First, the JPEG system builds upon previous work that showed that human perception focuses on low spatial frequencies [18]. Secondly, photographs exhibit guassian distribution of DC data and lapplacian distribution of AC data [19]. This means that less precision is required for different spatial frequencies, which the JPEG standard exploits. And thirdly, the difference between the DC representations of neighbouring parts of an image is more likely to be smaller than the absolute value of those DC representations. While more sophisticated human visual system models now exist based upon psychological and neurological research these advanced models would require more complex compression systems [20].

Due to its widespread use, and high levels of compression, JPEG is used by the Blackeye system.

Viewed algorithmically, JPEG compression is divided into 7 or 8 dis-

tinct steps [21]:

- 1. Convert from RGB to a luminescence-based colour system such as YCbCr. In greyscale images this step is not required.

- 2. The chrominance components of the image are reduced in spatial resolution, usually either 2:1 reduction in horizontal direction only, or 2:1 in both horizontal and vertical directions. In greyscale images this step is not required.

- 3. The pixels of each colour are grouped in blocks of  $8 \times 8$  pixels for further compression. If the resolution isn't a multiple of  $8 \times 8$  then extra pixels are inserted, copying the pixels of either the right or bottom edge. These blocks are called *minimum coding units* (MCUs).

- 4. A two dimensional discrete cosine transform (DCT) is performed on each MCU to produce an  $8 \times 8$  frequency map.

- 5. The data is quantised. This step is lossy; data is irretrievably lost. Each DCT coefficient is divided by a specific quantisation value then rounded to the nearest integer. These quantisation values are specified in a *quantisation table*. The JPEG standard provides recommended quantisation tables.

- 6. A variant of Huffman encoding is performed on each data unit. This may be replaced with arithmetic encoding.

- 7. Headers and requisite tables are added to the resulting file. The file format has multiple standards, the two most common of which are the JFIF and EXIF formats.

### 2.2.1 JPEG Modes

The JPEG specification is very flexible, allowing the encoders to choose from a range of options regarding the encoding process. The main options (indicated by bold type) are described as follows.

#### 2.2. JPEG ALGORITHM

There are four distinct modes of operation available to JPEG encoders: **baseline sequential**, **baseline progressive**, **lossless** and **hierarchical**. Lossless is self-explanatory. Hierarchical is used for storing multiple frames in a single file, where each frame's encoding depends on the previous frames (i.e. the kinds of processes used in video encoding). Sequential baseline mode, the most common [22], encodes the data entirely in independent  $8 \times 8$  data blocks, whereas baseline progressive performs DCT and quantisation operations on  $8 \times 8$  data blocks, but then performs entropy encoding upon groups of these data blocks.

Multiple **image components** are allowed per frame. These image components can be used to represent the colour space of the image; for example an RGB colour space would require three image components per frame (one for red, blue and green data samples). The JPEG specification does not provide for different colour spaces, relegating this task to the file format. However, it does provide example Huffman and quantisation tables for luminance and chrominance. The JFIF file format, for example, specifies the use of YCbCr colour space. The components need not be of the same sample rate, for example, chrominance pixel data may be binned while luminance pixel data stays at full resolution. This means that pixels in Bayer pattern form may be directly encoded. Only one image component is used for greyscale images. These image components may be interleaved (the first block of all image components is followed by the second block of all components) or not (all the blocks of the first image component are followed by all the blocks of the second component).

The specification allows for **8-bit** or **12-bit** sample resolutions. These resolutions apply to the pixel data components such as luminance and chromitacity.

The entropy coding stage (where the data compression occurs) may use one of two different techniques: **Huffman coding** or **arithmetic coding**.

While the JPEG standard allows for many different options, the application that this work is concerned with only requires the simplest JPEG implementation, namely 8-bit greyscale baseline sequential. Other aspects of the JPEG specification are ignored in the rest of this document.

### 2.2.2 Discrete Cosine Transform

The discrete cosine transform (DCT), sometimes referred to as the forward DCT to distinguish it from the inverse, is a discrete transform of data points to a sum of cosine functions. The DCT was first proposed in 1974 as a derivative of the discrete Fourier transform, and its potential application in image compression was immediately noted [23]. The transform has four main variants, but the JPEG standard specifies a variant of DCT-II [14]. The general DCT can be applied on a one-dimensional data array of arbitrary length, although multidimensional DCTs are derived from performing DCTs along each dimension sequentially. In the case of JPEG, the algorithm is further simplified because the data is always an  $8 \times 8$  block of data of integers in the domain [-128, 127]. Equation 2.1 shows the form used in the JPEG standard. The resulting  $8 \times 8$  matrix is a representation of the original MCU in the frequency domain. Note that element  $g_{0,0}$  is the DC element: it is  $\frac{1}{8}$  of the mean of the original MCU's pixels. The remaining elements are AC in nature and increase in frequency with their indices.

$$g_{u,v} = \alpha(u)\alpha(v)\sum_{x=0}^{7}\sum_{y=0}^{7}f_{x,y}\cos\left[\frac{\pi}{8}\left(x+\frac{1}{2}\right)u\right]\cos\left[\frac{\pi}{8}\left(y+\frac{1}{2}\right)v\right] \quad (2.1)$$

$$\alpha(u) = \begin{cases} \frac{1}{\sqrt{8}} & \text{if } u = 0\\ \frac{1}{2} & \text{if } u \neq 0 \end{cases}$$

#### 2.2.3 Quantisation

The quantisation stage of the JPEG algorithm is the lossy stage. DCT coefficients (the elements of an MCU after the forward DCT transform) are each divided by a constant, and the loss of information occurs due to maintaining integer level precision of the result.

The quantised matrix is the Hadamard product of the DCT matrix and some quantisation matrix. No quantisation matrix is specified by the JPEG standard, and therefore one must be included in the JPEG file for the decoder to use. It is usually represented as the array of elements by which the DCT matrix elements are divided, known as the quantisation table. While there is no standardised matrix construction system, Annex K of the JPEG Standard gives example chrominance and luminance quantisation tables as shown in Table 2.3. In 1991 the Independent JPEG Group (IJG) released one of the earliest open source JPEG software libraries, from which stems the quality system that is widely, though far from universally, used. IJG refers to the tables from Annex K as  $Q_{50}$ , indicating a 50% *quality factor*.

**Table 2.3:** The sample luminance quantisation matrix provided in Annex K of the JPEG Standard.

|            | 16 | 11 | 10 | 16 | 24  | 40  | 51  | 61  |

|------------|----|----|----|----|-----|-----|-----|-----|

|            | 12 | 12 | 14 | 19 | 26  | 58  | 60  | 55  |

|            | 14 | 13 | 16 | 24 | 40  | 57  | 69  | 56  |

| 0 –        | 14 | 17 | 22 | 29 | 51  | 87  | 80  | 62  |

| $Q_{50} -$ | 18 | 22 | 37 | 56 | 68  | 109 | 103 | 77  |

|            | 24 | 35 | 55 | 64 | 81  | 104 | 113 | 92  |

|            | 49 | 64 | 78 | 87 | 103 | 121 | 120 | 101 |

| $Q_{50} =$ | 72 | 92 | 95 | 98 | 112 | 100 | 103 | 99  |

|            | -  |    |    |    |     |     |     | _   |

Other quantisation tables are derived from  $Q_{50}$  by Equation 2.2 [24].

$$Q_x = \begin{cases} \frac{100-x}{50} \cdot Q_{50} & x \in (50, 100) \\ \frac{50}{x} \cdot Q_{50} & x \in (0, 50) \end{cases}$$

(2.2)

As discussed at the start of Section 2.2, lower frequencies are of greater significance than higher frequencies. This is reflected in this quantisation

table, which exhibits lower coefficients in the top left (low frequency) than in the bottom right (high frequency). Higher coefficients lead to smaller data values post quantisation which in turn are able to be further compressed than large values [25].

### 2.2.4 Entropy Encoding

This is the stage of the algorithm in which compression occurs. The two systems that can be used are Huffman encoding or Arithmetic encoding. Arithmetic encoding usually provides greater compression at the cost of further data processing. Huffman encoding, the one used in this project, is explained in further detail here.

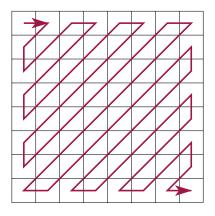

The order in which each element of an MCU is encoded is based upon a zigzag ordering, starting with the top left element and ending in the bottom right element. The diagram in Figure 2.3 depicts this.

**Figure 2.3:** Zig-zag ordering starting in the top left (0,0) and ending in the bottom right (7,7)

As mentioned above, the lower right is more likely to have runs of zeros and this ordering therefore clumps them together. Runs of zeros are the most compressible form of data in this type of Huffman encoding.

The DC elements (i.e. the first element of each MCU) is considered differently from the other elements. The DC value is replaced with the

difference between the current and the previous DC values. In general, photographs exhibit the frequent tendency of neighbouring MCUs having similar average intensities. Therefore the difference between DC values will often be small. Small values result in greater compression. Additionally, different Huffman tables are used for DC elements than those for AC.

Each encoded element consists of a code followed by a value (some values are of length 0). The code is from a Huffman table and specifies the length of value and the size of the run of zeros preceding the value. Huffman values are a form of binary representation where the length of the representation is important. This conversion is shown in the Table 2.4.

**Table 2.4:** Huffman value encoding table. This table compares the quantisedelement with its corresponding Huffman value.

| Value  | Quantised      | Values     | Huffman Values     |                    |  |  |

|--------|----------------|------------|--------------------|--------------------|--|--|

| Length | Quantised      | values     | Huffman values     |                    |  |  |

| 0      | 0              | 0          |                    |                    |  |  |

| 1      | -1             | 1          | 0                  | 1                  |  |  |

| 2      | -3, -2         | 2,3        | 00, 01             | 10, 11             |  |  |

| 3      | -7, -6, -5, -4 | 4, 5, 6, 7 | 000, 001, 010, 011 | 100, 101, 110, 111 |  |  |

| 4      | -15,,-8        | 8,,15      | 0000,,0111         | 1000,,1111         |  |  |

| 5      | -31,,-16       | 16,,31     | 00000,,01111       | 10000,,11111       |  |  |

| :      | ÷              |            | ÷                  | ÷                  |  |  |

| 11     | -2047,         | ,2047      | 00000000000,       | ,11111111111       |  |  |

DC elements are always at the start of an MCU, thus they do not have runs of zeros preceding them, so there is one Huffman code for each value length. As in the case of quantisation tables, these values are not specified by the JPEG specification, because each Huffman table will provide differing levels of compression for any given image. However, there are Huffman tables provided in Annex K of the specification that provide generally good levels of compression and are widely used. Table 2.5 shows the Huffman table for DC elements (the equivalent AC table is in Appendix A).

| Value Length | Code Word | Code Length |

|--------------|-----------|-------------|

| 0            | 00        | 2           |

| 1            | 010       | 3           |

| 2            | 011       | 3           |

| 3            | 100       | 3           |

| 4            | 101       | 3           |

| 5            | 110       | 3           |

| 6            | 1110      | 4           |

| 7            | 11110     | 5           |

| 8            | 111110    | 6           |

| 9            | 1111110   | 7           |

| 10           | 11111110  | 8           |

| 11           | 111111110 | 9           |

**Table 2.5:** Huffman Table: luminance DC coefficient differences (JPEG StandardAnnex K)

The table for AC elements is much longer as both value length and zero count are encoded. Quantised AC elements that are 0 do not have a corresponding Huffman output, but are only counted towards the current zero run. If 16 consecutive zeros occur there is a special code used and the zero run count restarts. If there are only zeros remaining in the current MCU, there is a special code (end of block) for terminating the MCU prematurely.

As an example to clarify this encoding: suppose the first MCU has DC element -16. This corresponds to a Huffman value of 01111 (Table 2.4). As it is value length 5 (the length in bits of the Huffman value) the Huffman table specifies the corresponding code word to be 110 (Table 2.5). Therefore, the entire Huffman code would be 110 01111.

The Huffman codes are concatenated into a single stream of data. The stream must be of an integer number of bytes in length, so if the number

28

of bits in the entire stream is not a multiple of 8 then the difference in bits is padded with 1's. Furthermore, as the byte 0xFF is used to indicate a marker in a JPEG file, any 0xFF that occurs in the data must have a 0x00 inserted after it.

### 2.2.5 File Format

The discussion in this section thus far has only considered the compression of images, not how the data is stored. JPEG image data is stored inside a file with extension .jpg or .jpeg, in a flexible format specified in the JPEG document. In addition to image data a variety of parameters are stored in the file specifying the specific implementation of JPEG being used, including quantisation and Huffman tables. There are two main JPEG file formats, EXIF and JFIF, both of which specify additional metadata that may be included [15].

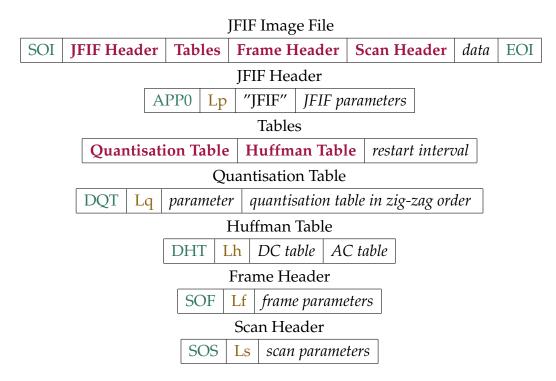

The diagram in Figure 2.4 shows the form that a JFIF file may take, and in this case it is of the simplest form, as used in this work.

Note that each section preceding the data starts with a JPEG-specified marker (always 0xFFXX), followed by 2 bytes that specifies the length of that section; when decoding the file only the data is of unknown length. The end of the data is signified by the end of image marker. As noted in Section 2.2.4, bytes in the data which are 0xFF have a 0x00 byte stuffed after them to prevent confusion with markers. If none of the parameters vary, then the entire file, less the data, may be hardcoded into the system producing the file.

#### 2.2.6 JPEG Summary

The JPEG specification [14] provides a standard to encode images. While it does have a lossless option, it is for the standard's lossy compression that it has been widely adopted for digital photographs. The Blackeye II uses a software library to encode images from its camera chip into JPEG-based

**Figure 2.4:** Example JPEG file containing in JFIF format. Standard JPEG markers XXX are 2 bytes. Length indicators Lx, also 2 bytes, indicate the length of each header or table in bytes.

files. This project implements a JPEG encoder on an FPGA to reduce the load on the microprocessor.

The unencoded data is in the form of a  $752 \times 480$  pixel image. Each pixel is represented by an 8-bit greyscale value, which is piped into the JPEG encoder along an 8-bit bus. This stream arrives row by row, left to right, rows starting at the top and going down. The encoder performs a baseline sequential greyscale encoding of the data which is stored in a JFIF file.

The encoder performs a 2D-DCT operation on  $8 \times 8$  blocks of pixels called MCUs. The DCT-MCU, also an  $8 \times 8$  block of data, represents the original MCU in a discrete frequency domain. A quantisation operation reduces the precision of the DCT-MCU, and in the process makes the en-

coding process lossy. The quantised-MCU is reordered and compressed by a Huffman encoder. The Huffman encoded data forms the JPEG data, which is encased in a JFIF file that adds metadata, such as, specifications of which JPEG mode was used, along with Huffman and quantisation tables.

# 2.3 Image Processing on FPGAs

Image processing has been an ongoing field of computing since 1957 [26]. Image processing techniques have made significant advances since then as computer hardware and software techniques have improved, and as early as 1991 researchers began developing imaging systems using FPGAs [27]. Hardware excels in a real-time system because the sheer number of operations that must be performed within a time frame preclude traditional software solutions. As images consist of many data points, the fetch-decodeexecute paradigm of CPUs results in excessive overhead compared with the parallelism of FPGAs [28]. This parallelism exists in images both spatially and temporally; different parts of frames can be processed simultaneously, and subsequent frames can commence while the current frame is still being processed [29]. Complex algorithms can be pipelined in an FPGA to respond to the requirements of real-time imaging systems, which include preprocessing, classification and encoding.

## 2.3.1 Image Processing Pipeline

The pipeline is made up of stages corresponding to operations. Some operations require longer pipelines than others. The length of the pipeline is the number of clocked registers the data must pass through from the start to the finish of the pipeline. This length is equal to the latency of the system; more specifically, the latency in clock cycles between data entering the pipeline and the corresponding data leaving the pipeline. A longer pipeline will result in a greater latency that may put pressure on any realtime constraints the system has.

A longer pipeline will also consume more hardware resources. Even stages of the pipeline that involve no operation, but only buffer, need resources: either the data are stored in LEs, in the FPGA's on chip block RAM, or on off-chip RAM. Off-chip RAM is limited by the bandwidth of its interface. This makes off-chip RAM inappropriate for use by several parts of the system (different buffers or operations). The different buffers must write and read from the RAM simultaneously. This may be possible with the appropriate type of RAM and a well-designed memory access system but this adds significantly to the complexity of the design. Thus off-chip RAM is of most use in the storage of a large amount of data at a single section of the pipeline.

On-chip block RAM is better suited for use by many operation buffers. As the name suggests block RAM is made up of many blocks of RAM, each highly configurable and able to be accessed independently. This means that it is usable by several parts of the systems at once, each part having a block, or multiple blocks configured to operate as required. The limitation is that any single block RAM can only be used by one RAM interface, meaning that any partially used block is wasteful. LEs are highly configurable, but the extent of their configurability means that much of their function is wasted if used purely for buffering. Thus both LEs and block RAM make suitable buffers for a pipeline but both are limited resources on an FPGA. Therefore adding many large buffers to a design will rapidly consume the FPGAs resources.

## 2.3.2 Image Processing Operations

Image processing operations can be broadly divided into three categories [28]: point operations, window operations and global operations. These refer to the portion of the image that each operation affects. Point operations are a mapping of one input pixel to one output pixel, whereas window operations take a sliding rectangle, or window, of pixels as input to produce an output pixel. Global operations are those that depend on data from the large parts, or the entirety of the frame. While all three of these types of operations may be performed on both CPUs and FPGAs, point and window operations are more suitable to FPGAs due to their short pipeline. Global operations with a much longer pipeline are more suited to software that is better suited to repetitive memory access systems.

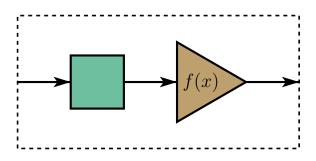

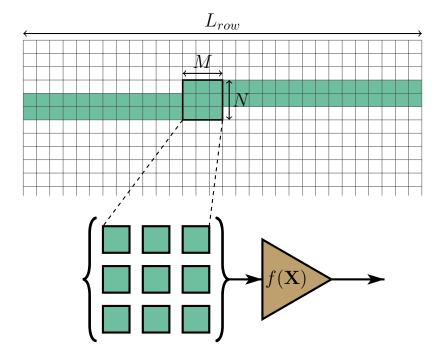

Point operations are the simplest image operation, they perform some function on each pixel individually. A simple example of this would be thresholding: values below the threshold are output as white, values above the threshold are black. To pipeline image operations the image should be processed serially, that is, going along each pixel on a row before starting to the next row, or less commonly going down column by column. This is simply a case of reading image data as it arrives, or sequentially from a buffer. Adding a point operation will usually involve a buffer of one pixel followed by the operation logic, as shown in Figure 2.5.

Thus the output of the point operation is a serial stream of pixel data with a 1 clock cycle delay, or *latency* of 1 relative to the input.

**Figure 2.5:** Point operation. Single pixel buffer followed by an operation results in a 1 clock cycle latency.

Window operators are more complex. Assuming that pixels are being received serially row by row, sufficient pixels must be buffered in order to obtain a window of the desired size. In reference to Figure 2.6, a window of size  $M \times N$  requires a buffer of (N - 1) + M pixels, as the window slides along and down the frame the buffer fills with the input pixels. The size of the buffer determines the latency as shown in Equation 2.3.

latency =

$$L_{row}(N-1)/2 + (M+1)/2$$

(2.3)

**Figure 2.6:** Window operation. In this example the window is 3x3, and the grid above shows the pixels of the frame that are buffered when the window reaches the point indicated.

Common window operators are linear functions; the output pixel is a weighted sum of the input pixels. An example of a linear window operation is a Gaussian blur [30].

#### 2.3.3 Summary of Image Processing

Image processing was identified as an application of interest early in the history of FPGAs. Many image processing operations are appropriate for acceleration in hardware due to their pipelinability. Operations that do not require an entire image, but only a part, called a window, are most suitable for efficient hardware implementation.

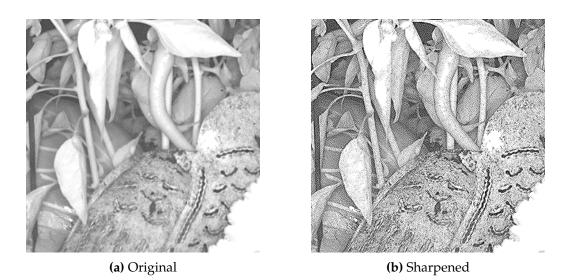

The Blackeye II system currently performs many image processing operations on its microprocessor. This project provides an architecture by which image processing operations may be implemented in hardware. To provide an example of this a simple linear window operation, an image sharpening filter, is included in the FPGA system.

# 2.4 Pre-existing FPGA-based JPEG Encoders

Commercial hardware designs for implementation in FPGAs (or other hardware systems such as ASICs) are available as intellectual property (IP) blocks. There are several companies offering JPEG encoder IP blocks. Information was able to be obtained about ones from Entner Electronics, VISENGI, CAST, Sundance Microprocessor Technology and Barco Silex [31, 32, 33, 34, 35]. IP blocks are offered under many licensing schemes: some use a royalty system, others use a one-off payment. Most provide the IP block as an encrypted file for addition to an FPGA project so that the source code is unavailable. Entner Electronics will provide you with the VHDL code of their system for extra cost.

Kinopta are wanting to trial a hardware-based image processing and encoding system in their cameras without having to fully commit themselves upfront to, what is for them, a new technology. For a small company, such as Kinopta, who aren't already committed to an FPGA based system the costs of these IP blocks can be prohibitively expensive.

The power requirements of Kinopta's camera systems is a major con-

cern of theirs. By not having access to the source code of any system they utilise, they are severely limited in their capability to optimise the system to their needs.

There are some open source JPEG encoder designs, these are free and provide the source code. However, most were too limited in their capabilities for this application. Furthermore, the licensing of most of these designs was too restrictive for Kinopta.

Despite these problems, these commercial designs are important reference points by which to compare JPEG encoder designs. Most of the examples mentioned provide their FPGA resource usage and advanced features. In the final chapter of this thesis these will be used in the evaluation of the JPEG encoder design.

# 2.5 Summary

An FPGA is a flexible digital system that can be configured to perform almost any digital logic. They can be used to great effect for operations that are inherently parallel. Paired with a CPU an FPGA may take the role of hardware accelerator: it provides addition processing capability for the CPU. This project uses an FPGA to perform image processing and encoding for a CPU to increase the system's performance.

Many image processing operations are parallel; each part of the image is operated on separately. Therefore, FPGAs have been identified as being good devices to perform image processing on. A pipeline can be formed on the FPGA so that while the first part of the image is undergoing the second operation, the next part of the image is undergoing the first operation.

The JPEG specification provides a standard to encode images. It performs compression to reduce the size of the image data and is widely used for digital photographs. The encoding process operates on  $8 \times 8$  pixels blocks called MCUs, which are first transformed into the frequency domain by a two dimensional discrete cosine transform (2D-DCT). The data is then reduced in precision and encoded by a Huffman encoder. The Blackeye II uses a software library to encode images from its camera chip into JPEG-based files. In this project an FPGA-based JPEG encoder is developed.

CHAPTER 2. BACKGROUND

# **Chapter 3**

# JPEG Encoder Implementation

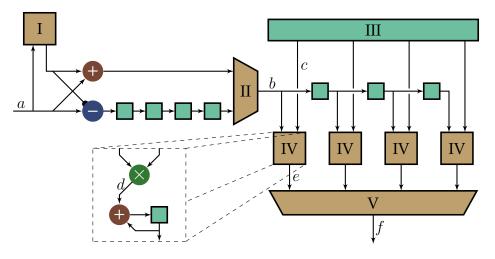

Since the JPEG standard was first announced many encoder and decoders have been developed in hardware. In recent years interest in JPEG encoders in FPGAs has increased for the reasons described in Section 2.1. JPEG encoders are partitioned into four stages to modularise the design process: 2D-DCT, Quantisation, Zigzag Buffer and Entropy Encoder [36, 37]. This chapter describes the design process of the JPEG encoder, and is partitioned into one section for each module. The subsequent chapter describes the design of the system in which the encoder is incorporated, adds further context to the encoder's design, and hence introduces further control mechanisms.

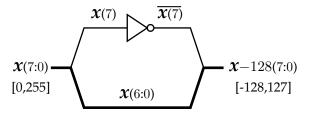

The JPEG algorithm, as described in Section 2.2, divides the frame up into  $8 \times 8$  blocks of pixels called MCUs. As each MCU is encoded sequentially the JPEG algorithm can form a pipeline: the first MCU begins encoding, and while it is still being processed the second MCU commences encoding. At this point it is assumed there is a constant stream of data. This stream is 8-bit parallel data, each representing a greyscale pixel value in the range [0,255], traversing an image row by row, from left to right and top to bottom. Before the data enters the encoder it must be converted from 8-bit unsigned data to 8-bit signed data appropriate for the DCT, within the range of [-128,127]. As per Figure 3.1, this conversion is completed in hardware by a single NOT gate. The output of this subtraction operation flows directly into the input of the DCT module.

**Figure 3.1:** Subtracting 128 from an unsigned 8-bit integer and converting it to an 8-bit two's compliment signed integer.

# 3.1 Discrete Cosine Transform

As described in Section 2.2.2, the JPEG variant of the DCT takes an input of an  $8 \times 8$  block of pixels, **F**, and outputs a frequency-based representation of the block as an  $8 \times 8$  matrix of values, **G**, as in Equation 3.1. A 2D-DCT is a process intensive operation; assuming the cosine terms are held in a look-up-table, each of the 64 elements requires the summation of 64 terms, each the product of 4 terms.

$$\mathbf{G}_{u,v} = \sum_{x=0}^{7} \sum_{y=0}^{7} \alpha(u) \alpha(v) \mathbf{F}_{x,y} \cos\left[\frac{\pi}{8} \left(x + \frac{1}{2}\right) u\right] \cos\left[\frac{\pi}{8} \left(y + \frac{1}{2}\right) v\right] \quad (3.1)$$

$$\alpha(u) = \begin{cases} \sqrt{\frac{1}{8}} & \text{if } u = 0\\ \sqrt{\frac{2}{8}} & \text{if } u \neq 0 \end{cases}$$

The 2D-DCT is, however, separable; two 1D-DCT operations may be performed on each dimension of **F** sequentially. The form of the onedimensional Equation 3.2 is still the same as Equation 3.1. In practical terms, a transitional matrix is produced by performing a 1D-DCT on each row of the input MCU, after which each column of the transitional matrix undergoes a 1D-DCT process, resulting in the 2D-DCT. By separating the two parts the hardware required to perform the transform can be simplified. Each 1D-DCT is simpler than the 2D-DCT, and by buffering the transitional matrix, the row-DCT, buffer and column-DCT form a pipeline ideal for a real-time hardware implementation.

$$\mathbf{g}_{u} = \sum_{x=0}^{7} \alpha(u) \mathbf{f}_{x} \cos\left[\frac{\pi}{8}\left(x+\frac{1}{2}\right)u\right]$$

(3.2)

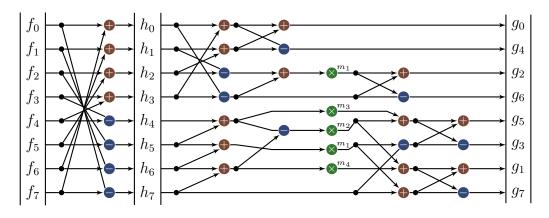

#### 3.1.1 1D-DCT Design

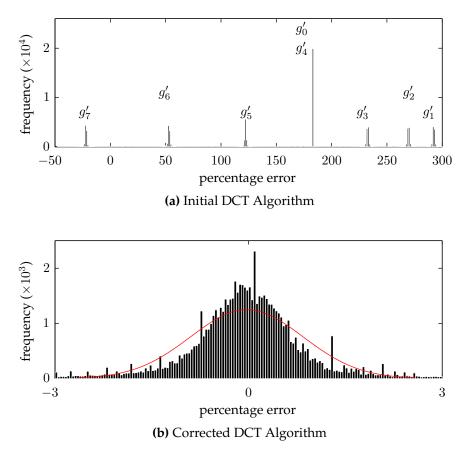

As the DCT algorithm is widely used throughout the field of image compression, there has been extensive study of its implementation since its conception. A very efficient algorithm for a JPEG-compatible DCT is that of Loeffler et al. [6, 38]. A scaled version of this algorithm is presented by Kovac and Ranganathan [39], which consists of a 1D-DCT with only 5 multiplications and 29 additions and subtractions as depicted in Figure 3.2 [6]. This already presents a huge advantage in reducing the computation over the regular form of the 1D-DCT, shown in Equation 3.2, that consists of 64 multiplications and 64 additions. As depicted in this figure, each element of the output vector, g, is a linear combination of the elements of the input vector, f. Another vector, h, is introduced in this figure as an intermediate between f and g. The elements of f are paired off, and the sums and differences of these 4 pairs constitute h as shown in Equation 3.3.

**Figure 3.2:** Scaled DCT. Constant multiplicands are  $m_1 = \cos\left(\frac{2\pi}{8}\right)$ ,  $m_2 = \cos\left(\frac{3\pi}{8}\right)$ ,  $m_3 = \cos\left(\frac{\pi}{8}\right) - \cos\left(\frac{3\pi}{8}\right)$ ,  $m_4 = \cos\left(\frac{\pi}{8}\right) + \cos\left(\frac{3\pi}{8}\right)$ .

$$\mathbf{h} = \begin{pmatrix} f_0 + f_7 \\ f_1 + f_6 \\ f_2 + f_5 \\ f_3 + f_4 \\ f_0 - f_7 \\ f_1 - f_6 \\ f_2 - f_5 \\ f_3 - f_4 \end{pmatrix}$$

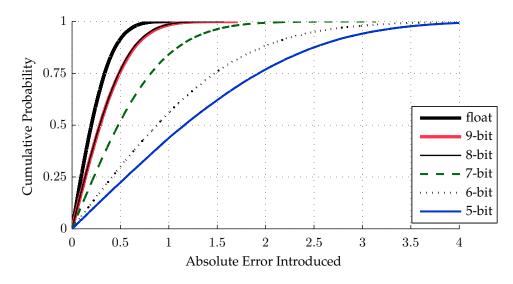

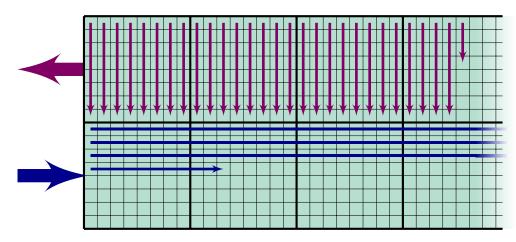

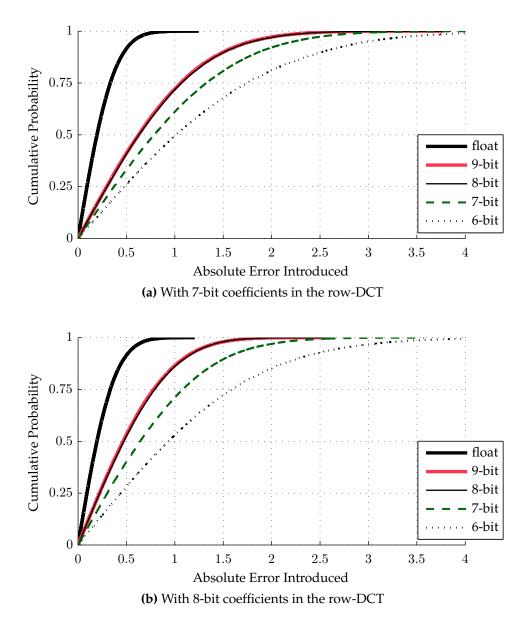

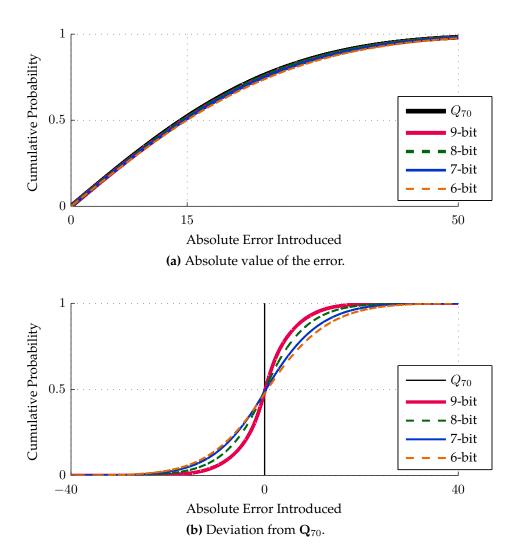

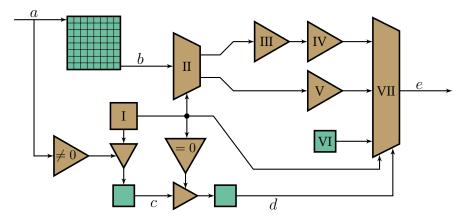

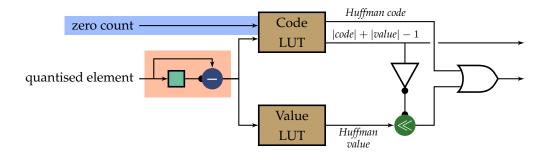

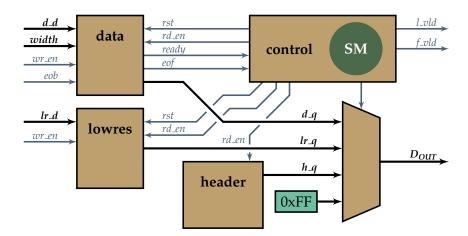

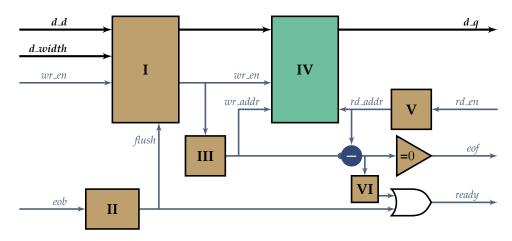

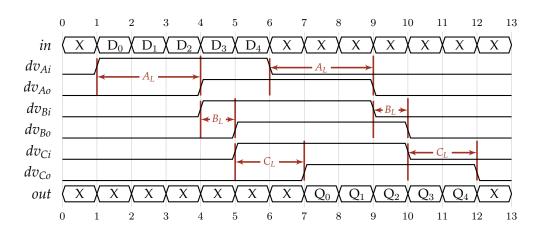

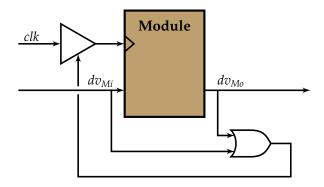

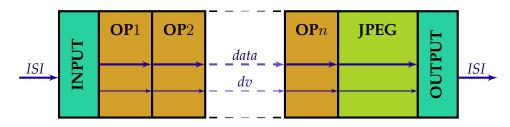

(3.3)