# Development of a PXI Express Peripheral Module and data transfer platform

by

Matthew David Bourne

A thesis submitted to the Victoria University of Wellington in fulfilment of the requirements for the degree of Master of Engineering in Electronic and Computer System Engineering.

> Victoria University of Wellington 2013

# Abstract

Magritek, a company who specialise in NMR and MRI devices, required a new backplane communication solution for transmission of data. Possible options were evaluated and it was decided to move to the PXI Express instrumentation standard. As a first step of moving to this system, an FPGA based PXI Express Peripheral Module was designed and constructed. In order to produce this device, details on PXI Express boards and the signals required were researched, and schematics produced. These were then passed onto the board designer who incorporated the design with other design work at Magritek to produce a PXI Express Peripheral Module for use as an NMR transceiver board. With the board designed, the FPGA was configured to provide PXI Express functionality. This was designed to allow PCI Express transfers at high data speeds using Direct Memory Access (DMA). The PXI Express Peripheral board was then tested and found to function correctly, providing Memory Write speeds of 228 MB/s and Memory Read speeds of 162 MB/s. Also, to provide a test system for this physical and FPGA design, backplanes were designed to test communication between PXI Express modules.

ii

# Acknowledgments

I would like to thank my supervisor Robin Dykstra for providing me the opportunity to undertake this project and his guidance over this time.

Thank you to my parents for their support and encouragement over the years to help me get where I am today. Especially to Dad for doing a last minute proofread of my entire thesis.

Lastly, big thanks to my flatmates at House Boston for their encouragement, support, feedback and for showing great patience when I bored them senseless with my musings and whiteboard scribbles on PCI Express, Address Spaces and Root Complexes. iv

# Contents

| 1 Introduction                |      |                                   |                             |                                             | 1                                         |  |  |

|-------------------------------|------|-----------------------------------|-----------------------------|---------------------------------------------|-------------------------------------------|--|--|

|                               | 1.1  | 1.1 Computers and Expansion buses |                             |                                             |                                           |  |  |

|                               | 1.2  | Instru                            | mentation                   | n                                           | 3                                         |  |  |

|                               | 1.3  | Motiv                             | vation of Project           |                                             |                                           |  |  |

|                               |      | 1.3.1                             | Magrite                     | k                                           | 3                                         |  |  |

| 2                             | Bacl | kgroun                            | d                           |                                             | 1<br>3<br>3<br>5<br>5<br>6<br>6<br>7<br>7 |  |  |

|                               | 2.1  | Preser                            | ent Magritek system         |                                             |                                           |  |  |

|                               |      | 2.1.1                             | Existing                    | Backplane                                   | 6                                         |  |  |

|                               |      | 2.1.2                             | Require                     | ments for new backplane                     | 6                                         |  |  |

|                               | 2.2  | Choice                            | e of new ]                  | Expansion Bus                               | 7                                         |  |  |

|                               |      | 2.2.1                             | _                           |                                             |                                           |  |  |

|                               |      |                                   | 2.2.1.1                     | VMEbus eXtensions for Instrumentation (VXI) | 7                                         |  |  |

|                               |      |                                   | 2.2.1.2                     | PCI Express eXtensions for Instrumentation  |                                           |  |  |

|                               |      |                                   |                             | (PXI Express or PXIe)                       | 7                                         |  |  |

|                               |      |                                   | 2.2.1.3                     | LAN eXtensions for Instrumentation (LXI) .  | 8                                         |  |  |

| 2.2.2 Evaluation of solutions |      |                                   |                             | ion of solutions                            | 8                                         |  |  |

| 2.3 PXI Express Overview      |      |                                   |                             |                                             | 9                                         |  |  |

|                               | 2.4  | Outco                             | comes and goals for Project |                                             |                                           |  |  |

|                               |      | 2.4.1                             | PXI Exp                     | ress Peripheral Module                      | 16                                        |  |  |

|                               |      | 2.4.2                             | PXI Exp                     | ress System Timing Board                    | 18                                        |  |  |

|                               |      | 2.4.3                             |                             |                                             |                                           |  |  |

|                               | 2.5  | 5 PXI Express description         |                             |                                             |                                           |  |  |

|                               |      |                                   |                             |                                             |                                           |  |  |

|                                   |     | 2.5.1   | PCI Exp          | ress                                       | 18 |

|-----------------------------------|-----|---------|------------------|--------------------------------------------|----|

|                                   |     | 2.5.2   | Instrum          | entation                                   | 20 |

| 2.6 PCI Express Architecture      |     |         |                  | chitecture                                 | 21 |

|                                   |     | 2.6.1   | Transact         | tion Layer                                 | 22 |

|                                   |     | 2.6.2   | Data Link Layer  |                                            |    |

|                                   |     | 2.6.3   | Physical         | Layer                                      | 24 |

|                                   |     |         | 2.6.3.1          | Logical Sub-Block                          | 24 |

|                                   |     |         | 2.6.3.2          | Electrical Sub-Block                       | 27 |

|                                   |     | 2.6.4   | Configu          | ration of Devices                          | 30 |

|                                   |     |         | 2.6.4.1          | PCI Configuration Space                    | 30 |

|                                   |     |         | 2.6.4.2          | PCI Enumeration and Configuration          | 34 |

|                                   |     | 2.6.5   | Packet T         | Transactions                               | 37 |

|                                   |     |         | 2.6.5.1          | Transaction Layer Packet                   | 37 |

|                                   |     |         | 2.6.5.2          | Data Link Layer Packet                     | 41 |

|                                   | 2.7 | FPGA    |                  |                                            | 43 |

|                                   |     | 2.7.1   | VHDL             |                                            | 47 |

|                                   |     |         | nal board design | 47                                         |    |

|                                   |     | 2.8.1   | Characte         | eristic Impedance                          | 47 |

|                                   |     | 2.8.2   | Length 1         | Matching                                   | 49 |

|                                   | 2.9 | Linux   | Systems          |                                            | 49 |

| 3                                 | Des | ign and | l Implem         | entation                                   | 51 |

|                                   | 3.1 |         |                  |                                            | 51 |

| 3.2 PXI Express Peripheral Module |     |         | -                |                                            |    |

|                                   |     | 3.2.1   | -                | ical requirements for board design         |    |

|                                   |     | 3.2.2   |                  | ress Power                                 | 56 |

|                                   |     | 3.2.3   | *                | ress Signals                               | 56 |

|                                   |     |         | 3.2.3.1          | PCI Express Transmit and Receive signals . | 57 |

|                                   |     |         | 3.2.3.2          | Clock Signal                               | 57 |

|                                   |     |         | 3.2.3.3          | Sideband Signals                           | 57 |

|                                   |     |         |                  | PCIe signals used for Peripheral Module    |    |

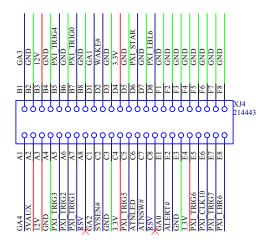

|     | 3.2.4                          | PXI Exp                                          | xpress Signals                               |     |  |

|-----|--------------------------------|--------------------------------------------------|----------------------------------------------|-----|--|

|     | 3.2.5                          | Creation of Libraries, Schematics and Footprints |                                              |     |  |

|     |                                | Device                                           | -<br>                                        | 63  |  |

|     | 3.2.6                          | Schemat                                          | ics                                          | 64  |  |

|     | 3.2.7                          | Complet                                          | ted board                                    | 68  |  |

| 3.3 | Desig                          | gn of System Timing Module                       |                                              |     |  |

| 3.4 | Imple                          | mentation of PXI Express system                  |                                              |     |  |

| 3.5 |                                |                                                  |                                              | 72  |  |

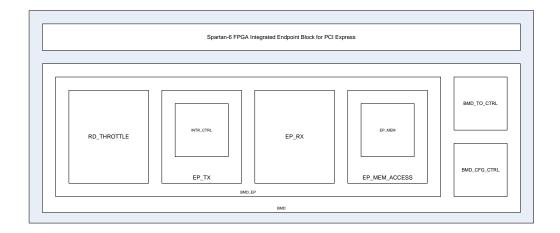

|     | 3.5.1                          | Spartan-6 FPGA Integrated Endpoint Block for PCI |                                              |     |  |

|     |                                | Express                                          |                                              |     |  |

|     | 3.5.2                          | Format of                                        | of PCI Express Design                        | 78  |  |

|     | 3.5.3                          | PCI Exp                                          | ress Data Transfer                           | 79  |  |

|     | 3.5.4                          | Program                                          | nmed Input/Output                            | 81  |  |

|     |                                | 3.5.4.1                                          | Example Xilinx PIO Design                    | 82  |  |

|     | 3.5.5                          | Direct M                                         | lemory Access Transmissions                  | 83  |  |

|     |                                | 3.5.5.1                                          | Xilinx Bus Master Performance Demonstra-     |     |  |

|     |                                |                                                  | tion Design for the Xilinx Endpoint PCI Ex-  |     |  |

|     |                                |                                                  | press Solutions                              | 84  |  |

|     |                                | 3.5.5.2                                          | Other PCI Express DMA solutions              | 86  |  |

|     | 3.5.6                          | Problem                                          | s and improvements to be made on sample      |     |  |

|     |                                | Xilinx de                                        | esigns                                       | 86  |  |

|     | 3.5.7                          | FPGA de                                          | esign for use on PXI Express Peripheral Mod- |     |  |

|     |                                | ule                                              |                                              | 89  |  |

|     |                                | 3.5.7.1                                          | Memory Unit                                  | 95  |  |

|     |                                | 3.5.7.2                                          | Receive Unit                                 | 98  |  |

|     |                                | 3.5.7.3                                          | Transmit Unit                                | 101 |  |

|     |                                | 3.5.7.4                                          | Implementation on FPGA                       | 105 |  |

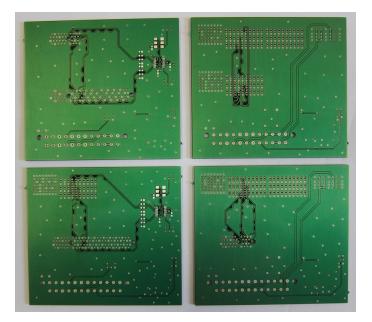

| 3.6 | Backplanes for testing devices |                                                  |                                              | 107 |  |

|     | 3.6.1                          | Power                                            |                                              | 110 |  |

|     | 3.6.2                          | Reset Circuit                                    |                                              |     |  |

|     | 3.6.3                          | Signal integrity                                 |                                              |     |  |

vii

|   |                               |        | 3.6.3.1                                 | Impedance Matching                            | 113 |

|---|-------------------------------|--------|-----------------------------------------|-----------------------------------------------|-----|

|   |                               |        | 3.6.3.2                                 | Length Matching                               | 116 |

|   |                               |        | 3.6.3.3                                 | Other steps                                   | 117 |

|   |                               | 3.6.4  | Compo                                   | nent Selection                                | 119 |

|   |                               | 3.6.5  | Comple                                  | ted PCBs                                      | 119 |

| 4 | Testing and Design Evaluation |        |                                         | 121                                           |     |

|   | 4.1                           | Testin | esting of PXI Express Peripheral Module |                                               |     |

|   |                               | 4.1.1  | Electrica                               | al testing of PXI Express Peripheral Module . | 121 |

|   |                               | 4.1.2  | Mechan                                  | ical testing of PXI Express Peripheral Module | 122 |

|   | 4.2                           | FPGA   | Designs                                 |                                               | 123 |

|   |                               | 4.2.1  | Test Cor                                | figuration                                    | 124 |

|   |                               |        | 4.2.1.1                                 | Test Configuration for SP605 Board            | 125 |

|   |                               |        | 4.2.1.2                                 | Test Configuration for designed PXI Express   |     |

|   |                               |        |                                         | Peripheral Module                             | 127 |

|   |                               | 4.2.2  | Softwar                                 | e for testing                                 | 128 |

|   |                               | 4.2.3  | PIO Des                                 | sign                                          | 132 |

|   |                               |        | 4.2.3.1                                 | Root Port Model                               | 132 |

|   |                               |        | 4.2.3.2                                 | Implementation on device                      | 134 |

|   |                               | 4.2.4  | 4 XAPP1052                              |                                               | 140 |

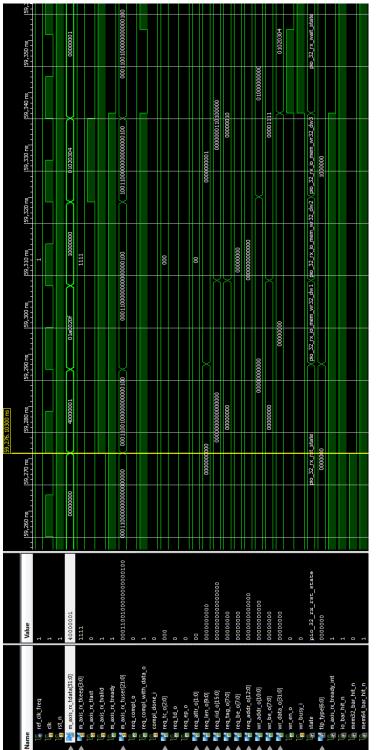

|   |                               | 4.2.5  | FPGA D                                  | Design for the PXI Express Peripheral Module  | 143 |

|   |                               |        | 4.2.5.1                                 | Testing on the SP605 board                    | 143 |

|   |                               |        | 4.2.5.2                                 | Implementation on designed PXI Express        |     |

|   |                               |        |                                         | module                                        | 144 |

|   |                               | 4.2.6  | Compai                                  | rison of designs                              | 147 |

| 5 | Conclusions and Future Work   |        |                                         | 149                                           |     |

|   | 5.1 Further Work              |        |                                         | 150                                           |     |

# Chapter 1

# Introduction

In this chapter, the historical environment for the project is given. This details the relationship between computers and expansion buses, an overview of instrumentation and lays out the motivation and reasons for the project.

# **1.1** Computers and Expansion buses

Computers are used in numerous areas of our lives for a number of different purposes. Each computer contains a Central Processing Unit (CPU) which acts as the brains of the device for a number of applications. A standard computer makes use of a CPU to take care of computations, random access memory (RAM) to save results of computations and data for currently used applications. Some basic Input/Output (I/O) to allow a user to interact with a computer is also used (such as a keyboard, mouse and screen). However, such a setup may not be enough for all applications as the users' needs may vary greatly. Some applications may require dedicated hardware, for example a lot of desktop computers come equipped with a video card to do the video processing. Less commonly, computers may come equipped with sound cards to take care of the sound processing. In the past, almost all computers did not have integrated video, sound or even network controllers on board. Instead, a peripheral card was required to provide this functionality. Recently, a lot of these commonly required functions have been either integrated on the computer motherboard, or even provided on the dye of the CPU. However for niche applications, such as an industrial test system, the functions and equipment required would not be provided out of the box, and need to be provided by an expansion card.

These peripheral devices require the ability to communicate with the CPU, either to be informed of operations or for memory to be read or written in either direction. The expansion bus is what takes care of this communication between peripheral devices and the CPU. In fact, many controllers embedded on the motherboard of a computer make use of the expansion bus standard for communication, even if the particular form factor is not used.

The first computer expansion bus, the S-100 bus or Altair bus, was part of the Altair 8800 which is considered to be the very first personal computer [1]. Here each board performed a particular function of the device. There were separate CPU, memory, I/O and video boards which fitted into a mainly passive backplane or motherboard.

The Altair and its variants were mainly hobbiest machines, although some small businesses made use of them. The first successful home computer, the IBM PC released in 1981 [2], used the Industry Standard Architecture (ISA) bus for expansion cards. This was the first concerted effort to standardise the interface bus. Its bandwidth and functionality were somewhat limited but it paved the way for future designs which are still used today.

ISA was later superseded by the Peripheral Communication Interconnect (PCI) standard [3]. This brought about plug and play functionality which meant no complex configuration was required to enable communication. Instead the host computer auto configures the system on start up.

This ability to send information between devices on a computer sys-

tem is an important aspect of the device. For specialist application test and measurement systems, some manufacturers choose to design custom solutions to have full control over the communication, whilst others design to standards to maintain interoperability with other devices.

Commonly, peripheral communication systems (such as PCI) use a card edge connector, plugging into a socket on the motherboard, which keeps the size small. Others use a socket-pin type connection which consumes more space, but can give a more reliable connection.

## **1.2 Instrumentation**

For most traditional PC applications which require an expansion card (such as graphics processing), timing is not a major factor. Due to this, the major PC peripheral interfaces PCI and PCI Express (PCIe) do not come with clock and trigger signals. However, quality instrumentation equipment does require this precise timing in order to get accurate measurements. Thus for instrumentation applications, whether a standard or custom solution, the backplane or motherboard will commonly come equipped with clock and trigger lines. These keep devices synchronised and are used to signal when particular events are to start or end.

# **1.3 Motivation of Project**

### 1.3.1 Magritek

Magritek is a company based in Wellington, New Zealand which uses technology developed at both Massey University and Victoria University of Wellington. Magritek develops compact Nuclear Magnetic Resonance (NMR) and Magnetic Resonance Imaging (MRI) devices for use in lab and field environments. A lot of the equipment is modular where a NMR or MRI system will make use of a number of different cards connected to the device. These cards may include RF transmitters, receivers etc. In order for effective communication and data transfer between peripheral cards, this requires a reasonable amount of bandwidth.

NMR is a physical phenomenon in which magnetic nuclei in a magnetic field absorb and re-emit electromagnetic radiation. Valuable information about the structure of the sample is gathered from the interaction between the magnetic moment of an atomic nucleus and an externally applied magnetic field. When an oscillating magnetic field is applied at a specific frequency (the Larmor frequency), transitions between different energy states (i.e. different orientations) occur. This is usually done by placing a coil around the sample to irradiate it with radio waves at the Larmor frequency. The nuclei in the sample absorbs these radio waves and re-emits them at the Larmor frequency. This emission is the NMR signal which can be detected by the antenna. Only nuclei with a non-zero magnetic moment - those with an odd number of protons or neutrons can undergo NMR.

Magritek presently makes use of their own custom backplane mechanism for the transfer of data between peripheral devices. However, it has limited bandwidth of around 5MB/s which is not sufficient for more advanced techniques such as multichannel MRI. Also, being a custom solution gives the limitation that their devices are not inter-operable with equipment manufactured by other companies. For these reasons, Magritek is looking to move to a new system for data transport. The purpose of this project was to develop some of the tools necessary to move in this direction.

# Chapter 2

# Background

In this chapter, the background of the project is described. This includes the choice of the PXI Express (PXIe) system, a brief description of the design direction chosen and an overview of important topics of this project. This includes details on the PXIe standard, FPGAs, high speed board design and the Linux environment.

# 2.1 Present Magritek system

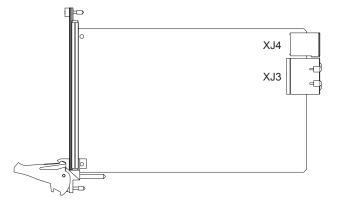

In order to perform the data capture for NMR, data needs to be sent between the various components of the system. A typical piece of Magritek NMR hardware consists of a chassis with add in cards which all perform a particular task. An example device is shown in Figure 2.1. This includes a DSP based host board which controls the applications on the device and can possibly interface with a PC. A typical data transfer would be when the host device sends a waveform file to the transmitter to output. Similarly, the receiver could send data after collection to the host board. Thus a transmission mechanism to perform these Memory Read, Memory Write transfers as well as control tasks is a crucial part of the system. Details on present backplane solution used by Magritek and the requirements for a replacement system are given below.

Figure 2.1: An example of a Magritek Spectrometer - The Kea 2 [4]

## 2.1.1 Existing Backplane

Communication between boards is presently provided using Magritek's custom backplane solution. Communication between the devices is typically provided by using address and data pins of the Digital Signal Processor (DSP). These get buffered and sent out along the backplane. This allows the DSP device to read or write to external devices. The Peripheral Modules of the Kea system meet a 3U form factor and are connected using a standard 96 pin connector. This is connected with the backplane using a socket-pin connection. For more sophisticated techniques such as multi channel MRI, the system does not provide enough bandwidth. Also the parallel format of data transfer meant the amount of expansion available was limited.

## 2.1.2 Requirements for new backplane

With increased bandwidth and expansion being much desired aspects, moving to a standard, well defined architecture was the approach chosen. The advantage of moving to a standard is that the communication system has already been designed so does not need to be developed from scratch. A form factor similar to their present system was desired so it would not involve too much chassis redesign. Thus a format which used pluggable expansion cards was required. The ability to send trigger and clock signals along the backplane was also required. Magritek's present devices are portable, rugged and used out in the field so a solution which provided these attributes was also desired. The intended architecture to be built for was x86 or ARM thus a peripheral bus which was supported by these architectures was required.

# 2.2 Choice of new Expansion Bus

The expansion bus industry was researched to find choices that fit the criteria. Some standard solutions such as PCI and PCIe provided increased bandwidth but did not give the desired form factor, or the trigger and clock signals required for instrumentation. Thus instrumentation buses were researched and evaluated. The choice was narrowed down to three options.

### 2.2.1 Instrumentation buses

#### 2.2.1.1 VMEbus eXtensions for Instrumentation (VXI)

VXI is an established open instrumentation standard which was adopted by the IEEE in March 1993 (IEEE 1155). It implements the VMEbus standard for data transfer bus which provides 320 MB/s throughput [5]. However VXI modules are either 6U or 9U in size which is larger than desired [6].

#### 2.2.1.2 PCI Express eXtensions for Instrumentation (PXI Express or PXIe)

PXIe is an instrumentation standard which evolved from the older PXI standard [7]. PXI used the older parallel PCI architecture for data trans-

mission, whilst PXIe moved to the newer PCIe standard. Cards meet the 3U eurocard form factor which is similar to the present Magritek design. The standard provides a plethora of high quality trigger and clock signals, both differential and single-ended. The use of PCIe as the transmission mechanism was somewhat future proof in terms of bandwidth availability. Further revisions of the PCIe standard have successively increased bandwidth where a maximum 250 MB/s is provided with revision 1.1 of the specification [8] and is now at 1GB/s as of version 3.0 of the specification [9]. It is a widely supported standard and is promoted by the PXI Systems Alliance whose sponsor members include two major instrumentation companies, Agilent Technologies and National Instruments.

#### 2.2.1.3 LAN eXtensions for Instrumentation (LXI)

LXI is an instrumentation and data acquisition standard using the Ethernet protocol to send data [10]. LXI is integrated with the PXIe standard where PXIe devices can communicate as a part of a larger LXI system. However, LXI is used more for distributed systems than standalone systems which was not the direction of this project.

### 2.2.2 Evaluation of solutions

All the standards are supported by major vendors so would allow add-in cards to be run across different devices. It was decided PXIe gave the best combination of portability, features and transmission speed. Also, PXIe devices are typically less cumbersome due to their 3U height rather than VXI's 6U height. As the data transport scheme of PXIe is essentially the same as PCIe, this provides greater bandwidth than the VXI system.

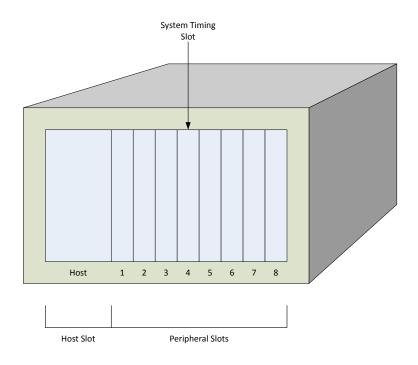

Figure 2.2: The layout of a typical PXI Express chassis

# 2.3 PXI Express Overview

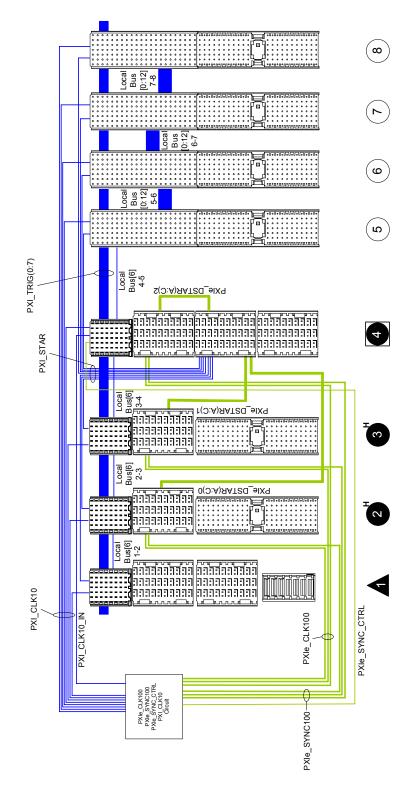

PXIe is an instrumentation standard which combines the PCIe serial transmission protocol with a more robust form factor and the addition of clock and trigger signals. An example PXIe chassis which houses these boards and provides the mechanism for trigger and clock signals to be sent between devices is shown in Figure 2.2. Peripheral devices thus get installed in this chassis and communicate through data being sent along the backplane. The backplane of this chassis distributes all the data, clock and trigger signals to the installed modules. A diagram of the distribution of these signals along an example backplane is given in Figure 2.3. Here, slots 1 through 4 show PXIe slots whilst slots 5 through 8 show legacy PXI slots.

Figure 2.3: Distribution of PXI Express signals on the backplane [11]

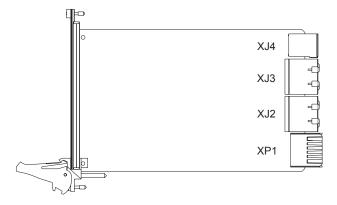

Figure 2.4: The layout of a PXI Express System Module [11]

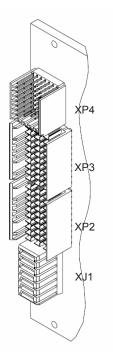

As can be seen in Figure 2.3, a PXIe system consists of PXIe System Module (situated at the far left of the chassis) which communicates with the other peripheral devices connected in the chassis. The layout of a PXIe System Module and System Slot are shown in Figures 2.4 and 2.5.

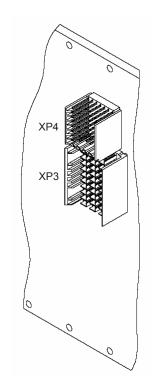

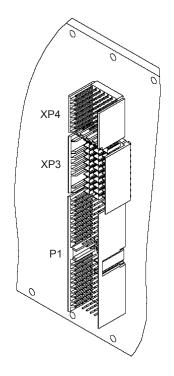

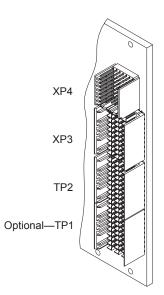

Peripheral devices are added by plugging a Peripheral Module into a Peripheral Slot or Hybrid slot on the chassis. The basic Peripheral Module, Peripheral Slot and Hybrid Slot are shown in Figures 2.6 to 2.8 respectively. Peripheral Slots only allow PXIe Peripheral Modules to connect whilst Hybrid slots also allow legacy PXI boards to be connected. PXIe systems commonly use Hybrid slots for the flexibility they provide.

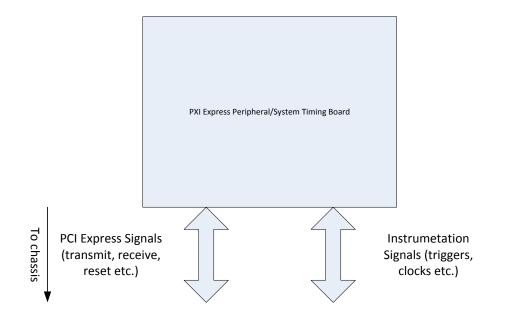

Lastly, the other allowable PXIe device is for System Timing purposes. The System Timing Slot is shown in Figure 2.9. The System Timing Board controls the timing of the device. This includes the distribution of star clock and trigger signals to the other peripheral modules.

# 2.4 Outcomes and goals for Project

PXIe is an excellent technology giving the best of high speed serial data transfer along with high quality clocking and trigger resources. Although it is an open standard its relatively niche use means that it is a rather un-

Figure 2.5: The layout of a PXI Express System Slot [11]

Figure 2.6: The layout of a PXI Express Peripheral Module [11]

Figure 2.7: The layout of a PXI Express Peripheral Slot [11]

Figure 2.8: The layout of a PXI Express Hybrid Slot [11]

Figure 2.9: The layout of a PXI Express System Timing Slot [11]

exploited market. As it stands, National Instruments and Agilent have become the two major players where they dominate the market. Thus the challenge was providing a device that met the standard at a relatively low cost and ease of use. Presently, if custom PXIe solutions are required, National Instruments provides the FPGA based FlexRIO board. This way the PXIe functionality is provided out of box. However, these are relatively high cost devices which do not offer much flexibility. If a high sensitivity design is required this would need a custom board design which could not be achieved using a breadboard or veroboard. Also, such a solution would only be useful for one off designs.

Test and Measurement has traditionally been an area where proprietary formats have dominated. Due to the complexity of the equipment, the high prices have just been attributed as a fact of the devices. However, there is a definite opening in the market if PXIe devices could be offered at a lower price point. An open source system could be provided with a basic board design, FPGA design and device driver. The challenge was making a high performance open system where no purchased IP had to be used. Thus the major cost of the device would be the board construction and components used, rather than requiring any purchased IP from outside of the company, producing devices at the lowest cost possible.

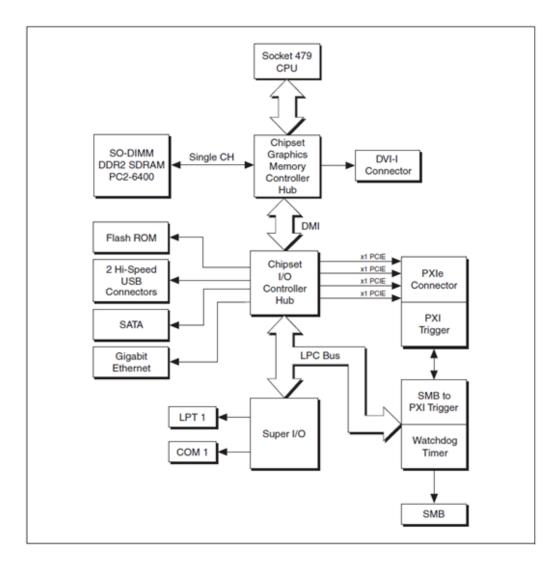

PXIe devices include a system controller card which includes the CPU, RAM and I/O which the user makes use of to communicate with the device. Magritek's present devices use a similar format where the user communicates with a host board which in turn communicates with the peripheral devices. The move to PXIe would allow for an ARM processor based PXIe System Module to be designed in the future. ARM processors are low cost, low power devices for which PCIe solutions are available [12].

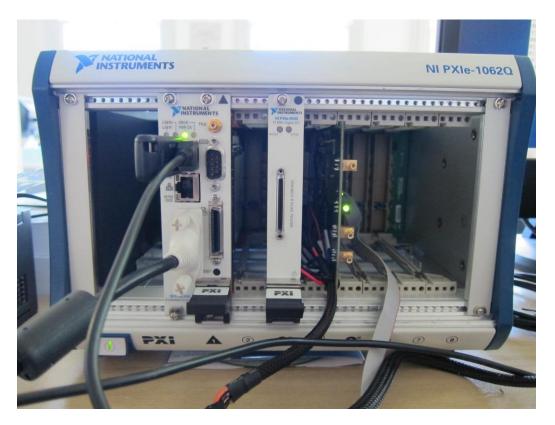

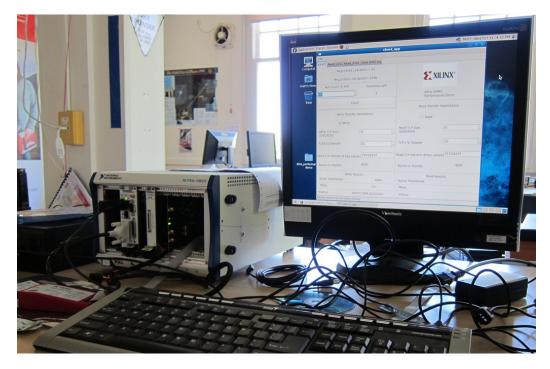

A PXI Chassis complete with a PXIe System Module was required to communicate with peripheral devices. For this, a National Instruments (NI) PXIe-1062Q chassis fitted with a NI PXIe-8101 Embedded Controller card was sourced. The PXIe-1602Q chassis is shown in Figure 2.10. The

Figure 2.10: National Instruments NI PXIe-1062Q Chassis [13]

connectors on the backplane indicate this chassis came equipped with slots for two Peripheral Modules and a System Timing Board. It also had slots for older, legacy PXI cards. However, these were not the direction of the project and were largely ignored.

The move to this open PXIe standard involves a number of steps including the development of a PXIe chassis, controller card and Peripheral Module. The first step in moving to this system was producing a PXIe Peripheral Module for NMR use which is detailed below.

## 2.4.1 PXI Express Peripheral Module

For this project, the design and implementation of a PXIe Peripheral Module was focussed on. The Peripheral Module would operate as a NMR transceiver. The device was based off a present Magritek device which makes use of the custom backplane. The device were adapted to meet the PXIe standard as well as adding improved Digital to Analog Converters (DACs), Analog to Digital Converters (ADCs) and other features.

As well as developing the physical PXIe Peripheral Module, the PXIe communication on board had to be implemented. The base PCIe functionality can be provided using a dedicated IC [14]. In this case, the required PCIe signals get connected directly to the IC which takes care of the PCIe link. However, this would then have to be interfaced with the rest of the logic on board which would complicate the board design.

The PXIe configuration can also be performed by an FPGA. FPGAs (which will be covered in further detail later) allow dedicated logic blocks to be implemented. No FPGA vendor provide complete PXIe solutions, however Xilinx and Altera both provide PCIe solutions for their devices [15, 16]. These have the potential to reduce development time and simplify the board design as few external ICs would be required, and everything could be configured inside the FPGA.

Implementing the PXIe protocol on an FPGA was decided as the best design option. It simplified the board design and made development of the PXIe system simpler. Magritek's present devices all make use of FPGA designs so this would allow the fastest development time for a PXIe Peripheral Module for NMR applications.

The physical device along with the FGPA design was intended to meet to following requirements.

- Used a Xilinx FPGA (specifically the Spartan-6) as the controller of the board.

- An open PCIe FPGA design system where no purchased or nodelocked IP was used and all source code was available.

- Open source device driver and application used.

## 2.4.2 PXI Express System Timing Board

A PXIe System Timing Board was also designed, which would control the timing, clocks and triggers to the peripheral devices. It also met the requirements given for the Peripheral Module.

### 2.4.3 Backplanes to test devices

Along with the boards, test backplanes were designed to test designed modules along with FPGA based PCIe development kits. These would allow communication between a host and peripheral system to test that the devices were working as required. The test backplanes were designed to test PXIe modules as well as standard PCIe boards.

# 2.5 PXI Express description

As explained earlier, PXIe can be seen as the instrumentation extension of the PCIe serial transmission protocol. Thus data is sent in the same way as a PCIe transaction. The description of the standard has been broken into a description of the PCIe data transmission system and the instrumentation signals which make up the PXIe standard.

### 2.5.1 PCI Express

For more than a decade in computer technology, the preferred computer bus for hardware devices was Peripheral Component Interconnect, most commonly known as PCI. This became the standard for expansion cards in the mid 1990s where it provided much higher bandwidth than the older ISA standard of the time [17]. PCI is a parallel architecture which has a max transfer rate of 133 MB/s, 266 MB/s or 533 MB/s depending on the frequency and bus width [3]. Peripheral devices are connected to this PCI

#### 2.5. PXI EXPRESS DESCRIPTION

bus which can host up to five devices reliably. Whilst this provided adequate bandwidth up until the late 1990s, the turn of the decade brought about the requirement for dedicated high bandwidth which PCI could not provide. This was due to number of reasons, one being the limitations inherent in the parallel format. This meant that frequencies could not be pushed much higher than that which were presently used without massive changes to board design. Also, the shared bus meant that dedicated bandwidth was not provided. The maximum bus transfer rate was shared between all devices.

To get around these problems in PCI, a new transmission system was devised in PCIe which was released in 2004 [8]. Here, devices are connected through a high speed serial connection. Each device has a connection to the central controller, known as the Root Complex. This is provided either directly or through a bridge. They do not share data and address lines as seen in PCI, so there are no limitations on concurrent access across multiple Endpoints. The serial scheme uses dedicated upstream and downstream links which use differential signalling. Data can be sent and received simultaneously, known as full-duplex transmission.

PCIe is a packet based technology where all information is sent across the same link. There is no need for separate address, data, control, interrupt or clock signals resulting in much more efficient use of ports. Also, the design of PCIe allows for more bandwidth when required. A PCIe link is built around couples of differential serial point-to-point connections known as lanes. More lanes can be provided to give more bandwidth when the application requires it. Revision 1.1 of the specification states that along one lane, 250 MB/s is provided [8]. If only one of these lanes is used, this would give a x1 PCIe link. A graphics card usually makes use of a 16 lane (or x16) link which gives 4GB/s bandwidth in the 1.1 specification. This scalability allows a variety of devices, each with their own bandwidth demands, to be used over a PCIe link. For instance, a device may not require extremely high data speeds, but does need the dedicated bidirectional bandwidth which PCIe provides. For such a device, a x1 link would be adequate.

Though PCIe was designed to succeed PCI, it was also designed so the two maintained compatibility. As of 2012, PCI devices are still being produced. Some devices do not require the increased bandwidth PCIe provides and have opted to stay with the older PCI system. The two remain interoperable through software compatibility. PCI was the industry standard for around ten years and brought with it a lot of strengths. PCIe performs configuration in a similar method to PCI. They both make use of the PCI Configuration Space. This is the underlying way that devices get automatically configured when inserted into the bus. This is known as plug-and-play. However it is implemented in such a way that compatible devices can also make use of the more advanced PCIe features.

### 2.5.2 Instrumentation

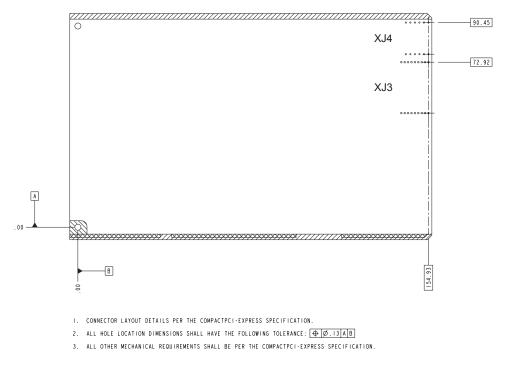

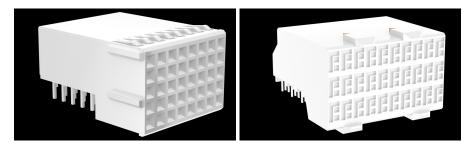

Where a PXIe design differs from a standard PCIe design is that it is an instrumentation module which comes in a much different form factor and includes additional signals. PXIe uses the form factor specified by CompactPCI Express (cPCIe) standard and provides additional instrumentation signals. The cPCIe form factor uses metric spacing and gives a more robust mechanical form factor than desktop PCI.

The connector design defined in the standard specifications of PCI and PCIe is fit for use in standard desktop computers. However, such a design does not meet the requirements for industrial applications. Due to this, the form factor CompactPCI was developed as an extension to PCI and the specifications released in 1997 [18]. The advantages over conventional PCI include a vertical card orientation for improved cooling, improved shock and vibration characteristics, high performance, and robust connectors.

When used for instrumentation applications, the connectivity provided by CompactPCI still had some limitations. Whilst the CompactPCI form factor is a lot more rigorous than PCI, a lot of measurement and automation systems require precise timing which CompactPCI cannot provide. For this reason, the PCI eXtensions for Instrumentation (PXI) standard was developed and released, also in 1997. This format takes the advantages of the CompactPCI form factor and provides timing, synchronization and triggers to be sent along the backplane [19].

With the development of PCIe, the benefits of the new technology were desired in a more robust form factor. The cPCIe specification was released on June 27, 2005 [20] which was soon followed by the PXIe (PXIe) standard [11]. PXIe also improves on the clocking and triggers provided in the original PXI standard by providing higher performance differential clocking and trigger signals.

PXI and PXIe provide various clocking and triggering signals to the system for use in instrumentation applications. These devices usually include a central System Timing card which controls length matched (or star) trigger and clock signals to the other peripheral cards where this is required.

As well as the form factor, these described systems also differ from a traditional PC as the CPU and memory are not found on the motherboard. Instead, cPCI, cPCIe, PXI and PXIe all include a System Card which houses the CPU, memory and hard drive for the system. This card also drives the clock source to the peripheral cards for their PCIe interconnect. Thus the backplane in these systems is much more passive than a standard PC motherboard.

# 2.6 PCI Express Architecture

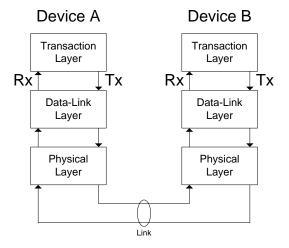

The system architecture can be explained using a three layer abstraction model which is shown in Figure 2.11. The three layers which build a PCIe transaction are the Transaction Layer, the Data Link Layer and the Physical Layer. The serial architecture is packet based where each layer deals with

Figure 2.11: The three-layer abstraction of the PCI Express protocol

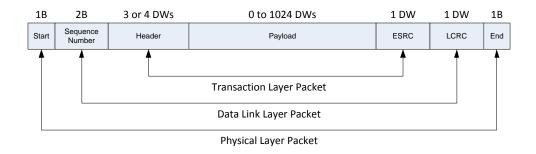

a different level of the packet, like a typical network stack. These layers become encapsulated in one another which is shown in Figure 2.12. These layers and their interactions are detailed below.

### 2.6.1 Transaction Layer

The top layer of the PCIe protocol is the Transaction Layer. It receives requests or data packets from the device core and serves as the starting point for turning these into PCIe transactions. The Transaction Layer (TL) does this by creating a Transaction Layer Packet (TLP) as shown in Figure 2.12. This comprises of a header which outlines the details of the packet, a data payload and an optional end-to-end cyclic redundancy check (CRC) which is used to test the integrity of the TLP. As well as starting the process for PCIe transactions on the transmission side, it also provides the reverse process on the receiving side where it passes the data on to the device core in the correct format.

Figure 2.12: The encapsulated design of the PCI Express packet structure

For example say the core of some device A decides it wants to read the memory of device B. The Transaction Layer turns this information into a Memory Read Request and sends this packet onto the Data Link Layer. Later, the Transaction Layer of device A receives a completion packet from device B. This is passed up from the receive side of Data Link Layer which the Transaction Layer then decodes and passes this data on to the device A core.

#### 2.6.2 Data Link Layer

The middle layer of the PCIe protocol is the Data Link Layer (DLL). The function of the DLL is to keep the link performing well and provide error detection and correction. After packets are created in the Transaction Layer, they get passed along to the DLL which adds a sequence number and LCRC error checker. This then gives a Data Link Layer Packet (DLLP). Thus, when packets get received, the Data Link Layer checks their integrity by verifying the CRC. The sequence number is also checked to ensure the packets have arrived in the correct order.

As well as further encapsulating TLPs, the DLL also generates its own packets to perform particular tasks it is responsible for. These tasks performed in the DLL include flow control, power management and ensuring

Figure 2.13: Physical Layer of PCI Express

reliable delivery of TLPs between Endpoints via acknowledgements.

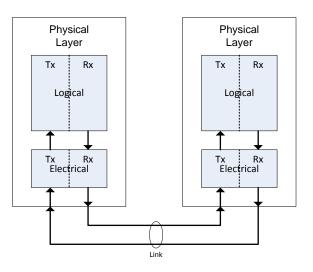

## 2.6.3 Physical Layer

The Physical Layer provides the digital and analogue circuitry necessary to configure and maintain the link [17]. The Physical Layer comprises of two different sub-blocks: the Logical and the Electrical sub-blocks as shown in Figure 2.13. These are detailed below.

## 2.6.3.1 Logical Sub-Block

The transmit function of the logical sub-block provides four important processes: data scrambling, 8-bit/10-bit encoding, packet framing and serialisation. The receive function is to provide the reverse processes.

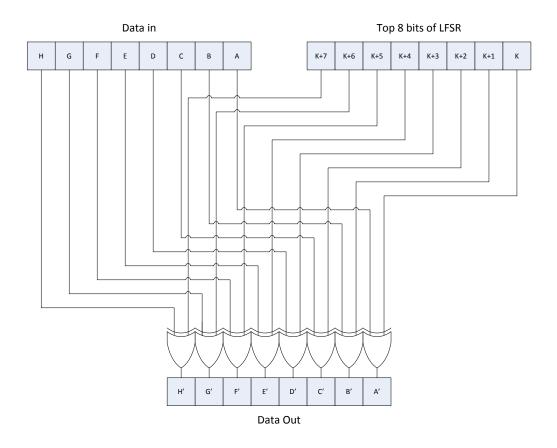

**Data Scrambling** Data scrambling is used to reduce the possibility of electrical resonance on the link. Resonance is usually caused by repeated patterns or bit sequences. Scrambling breaks up these repeated patterns

Figure 2.14: PCI Express Data Scrambler

meaning no single frequency component is transmitted for a long period of time. This spreads the frequency spectrum resulting in a 'whitening' of the bit stream (known as spread-spectrum). The scrambling is done by performing an XOR operation on the data with a pseudo-random number generator, implemented using a Linear Feedback Shift Register (LFSR). On the receive side this data is then descrambled using another LFSR. Synchronisation between LFSRs so that the same data is received on both sides of link is performed on start up. This scrambler is shown in Figure 2.14.

**8b/10b Encoding** Encoding is also applied to the data in the logical subblock. This is used to embed the clock cycle into the data stream which

eliminates the need for an external clock signal to recover the data. Due to this embedded clocking, the same stringent routing required in PCI is no longer necessary. In a parallel system such as PCI, there is a strict requirement that all signals must arrive at the same time or a mismatch will occur. To meet this requirement, signal lines are snaked across the board to keep the track lengths the same meaning signals reach the destination at the same time. The problem becomes exacerbated at higher frequencies, where very small differences in track lengths can correspond to signals being one or two bits out of phase with one another. It is for this reason that PCI cannot be pushed much further than 33 MHz it operates at. With the serial, embedded clock system of PCIe, the same timing problems are not apparent which allows much higher frequencies to be used. It also improves board routing, as signals do not have to be snaked which saves board space and simplifies the routing process.

The encoding also provides DC balance on the data line as it keeps the number of 1s and 0s as equal as possible. Removing the DC component prevents capacitance along the lane from being over charged. This means the ability to change from one logic level to another is not hindered which therefore reduces inter-bit interference.

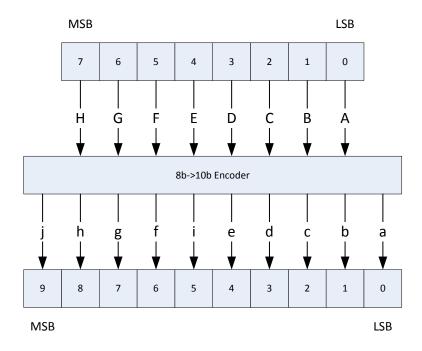

In the PCIe 1.1 specification the encoding is performed using 8b/10b encoding where every 8 bits of data was encoded to a 10 bit data stream. This forces a minimum number of bit-level transitions within a particular signal. The 8-bit/10-bit encoding format allows at most five bits of the same polarity to be transmitted before a bit transition must occur. This gives sufficient 0-to-1 and 1-to-0 transition density so that the clock signal can be recovered on the receive device using a phase-locked loop (PLL). It is performed by breaking a byte up in to a five-bit block and a three-bit block which get encoded to a six-bit block and four-bit block respectively using table lookups. The encoding, whilst adding a 25% overhead to the transmission, is worth it for the benefits gained from embedded clocking. A description of the 8b/10b encoding scheme is given in Figure 2.15. The

Figure 2.15: 8b/10b Encoding

reverse of this process is applied on the receive side to decode the original data. Encoding is used in all versions of the PCIe protocol. A similar process, but with less overhead, is used in PCIe 3.0 which uses 128b/130b encoding [9].

#### 2.6.3.2 Electrical Sub-Block

The electrical sub-block functions as the delivery mechanism along the physical link. On the transmit side this consists of converting the serial bit stream to electrical signals to send on along the link. The receive side detects this electrical signalling and recreates the bitstream.

One of the major limitations of PCI is its use of single ended signalling where all signals are referenced to ground. Noisy ground planes can effect the signal integrity. At high frequencies the noise generated increases as do the attenuation effects, thus PCIe employs a different type of signalling.

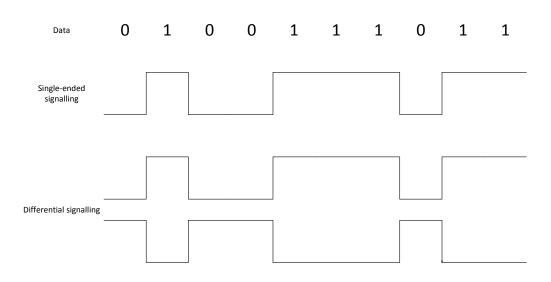

Figure 2.16: Comparison of single ended and differential signalling

The transmission scheme is known as high-speed Low-Voltage Differential Signalling (LVDS). This is where the signal is representing by the difference between two signals (a differential pair). The difference between single ended signalling and differential signalling is shown in Figure 2.16. A PCIe differential pair consists of two signals, D+ and D-. A logical one is sent out by driving the D+ lane high and the D- lane low and a logical zero is signalled by driving the D+ signal low and the D- signal high. In this way, no ground reference is required which provides greater signal integrity and noise immunity.

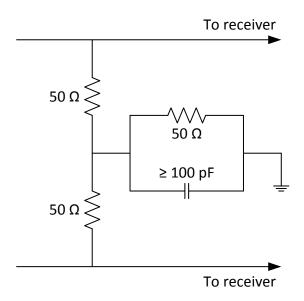

The high frequency differential signals also make use of a balanced transmission line. This is employed in the PCIe LVDS transmission scheme. The characteristic impedance of a link is  $100 \Omega$ . Balancing the transmission lines helps the rejection of external noise in the circuit and minimise reflections along the link. This is matched to the transmitter and receiver.

To prevent any DC offset voltage appearing on these differential lines, PCIe requires a decoupling capacitor to be used on the transmit side of the differential pair. The decoupling is provided using a 75 to 200 nF capacitor either on the PCIe device itself or on the motherboard. This greatly simplifies the buffer design for PCIe devices as they do not receive signals which have a large DC offset.

In the PCIe Revision 1.1 specification, the bitrate of transmission is 2.5Gb/s. To meet requirements this clock needs to be accurate to 300 ppm jitter about its centre frequency [8]. This clock is usually derived from a 100 MHz clock signal distributed along the system board which is then multiplied to 2.5GHz by way of a PLL. This 2.5GHz clock does create some EMI radiated noise however, and so the option of Spread spectrum clock-ing (SSC) is given. This prevents a noise spike at 2.5GHz by spreading over a small frequency range about 2.5GHz by way of a small 0% to -0.5% modulation using a modulation rate between 30KHz and 33KHz.

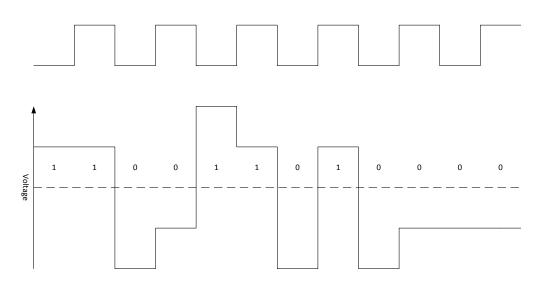

As PCIe operates at very high frequencies, the period of each bit is very small. Thus the capacitive effects on the link are very apparent. This can cause inter-symbol interference (ISI) where a change in the polarity of the bit can be effected by the previous bit(s). In order to overcome this, a method known as de-emphasis is used. As detailed earlier, the number of consecutive bits allowed is 5. Say for example that five logical 0s are sent across the link, followed by a 1 and then another 0. Because of capacitance on the link, transition to the 1 may not happen quickly enough to register the logical 1 occurred before the next 0. The use of de-emphasis means that every new bit (i.e. one that was different from the one that came before it) would be transmitted at a higher power than any subsequent bits of the same polarity. For example, the signal transmitted five 0s in a row and then a 1, the four 0s that follow the first one would be at reduced power and then a boosted power 1 would be sent. This allows the system to discharge faster and thus the 1 can be transmitted successfully, overcoming any issues with ISI. An example of this de-emphasis system is shown in Figure 2.17. As can be seen, on every bit transition from 0 to 1 or 1 to 0, a boosted voltage is used. Then for any bit which is the same polarity as the previous bit, the standard voltage level is used.

Figure 2.17: Description of de-emphasis system

## 2.6.4 Configuration of Devices

One major strength of PCI was its software mechanism which brought plug-and-play, the ability to add a new component to a system without requiring manual configuration. PCIe kept this system which makes use of the PCI Configuration Space. The PCI Configuration Space, enumeration and configuration are detailed below.

#### 2.6.4.1 PCI Configuration Space

The PCI Configuration Space is how PCI and PCIe devices are initialised and configured for use in the system. This is a space with standardised registers which allows the auto configuration of Peripheral Modules through the reading and writing of particular registers. The format of the PCI Configuration Space depends on the type of device. The Configuration Space Header for a PCI Type 0 (Non-Bridge) device is shown in Table 2.1.

The Device ID and Vendor ID are useful for the operating system to detect the particular device installed. The Vendor ID is a particular code which PIC-SIG members are provided to identify their devices. The De-

| Bits [31-24]                   | Bits [23-16] | Bits [15-8]      | Bits [7-0]      | Reg  |  |  |  |  |

|--------------------------------|--------------|------------------|-----------------|------|--|--|--|--|

| Devi                           | ce ID        | Veno             | dor ID          | 0x00 |  |  |  |  |

| Sta                            | itus         | Com              | mand            | 0x04 |  |  |  |  |

|                                | Class Code   |                  | Revision ID     | 0x08 |  |  |  |  |

| BIST                           | Header Type  | Latency Timer    | Cache Line Size | 0x0C |  |  |  |  |

|                                | Base Address | Register 0 (BAR  | ))              | 0x10 |  |  |  |  |

|                                | Base Address | Register 1 (BAR  | 1)              | 0x14 |  |  |  |  |

|                                | Base Address | Register 2 (BAR  | 2)              | 0x18 |  |  |  |  |

| Base Address Register 3 (BAR3) |              |                  |                 |      |  |  |  |  |

|                                | Base Address | Register 4 (BAR4 | 0x20            |      |  |  |  |  |

|                                | Base Address | Register 5 (BAR  | 5)              | 0x24 |  |  |  |  |

|                                | Cardbu       | s CIS Pointer    |                 | 0x28 |  |  |  |  |

| Subsys                         | stem ID      | Subsysten        | n Vendor ID     | 0x2C |  |  |  |  |

|                                | Expansion R  | OM Base Addres   | s               | 0x30 |  |  |  |  |

|                                | Reserved     |                  | Revision ID     | 0x34 |  |  |  |  |

|                                | Re           | eserved          | •               | 0x38 |  |  |  |  |

| Max latency                    | Min Grant    | Interrupt        | Cache Line Size | 0x3C |  |  |  |  |

Table 2.1: PCI Configuration Space Header for a PCI Type 0 (Non-Bridge)

Device

vice ID is a description of the function of the device. These together give the "PCI ID" and together identify the device model. The Vendor ID is the chip manufacturer and the Subsystem Vendor ID is the card manufacturer.

The Header Type describes the remaining 48 bytes of the header, depending on the function of the device. Type 1 headers are for the Root Complex, switches and bridges. PCIe Endpoints are Type 0.

The Base Address Registers (BARs) are used to inform the device of its address mapping by writing configuration commands to the PCI controller.

PCIe makes use of the standard PCI Configuration Space and extends it to include special PCIe functions. The standard 256 bytes of PCI Configuration Space can be used by legacy operating systems which do not support the advanced features. All PCIe devices must implement the PCI 3.0 Compatible Configuration Space Header and the PCIe Capability structure inside this 256 bytes of configuration space. As well as the PCI Express Capability structure there are also further registers known as the PCI Express Configuration Space, past the first 256 bytes. These are known as the PCI Express Extended Capabilities. This must start immediately after the 256 byte PCI Configuration Space. Here pointers are included to the rest of the registers which include, serial number and power management registers. This configuration space (including the 256 bytes PCI Configuration Space) is 4KB in total. A diagram of this layout is given in Figure 2.18

Inside the PCI Express Capability structure are parameters that are necessary for PCIe transactions, that are not required for standard PCI devices. As with the standard PCI Configuration Space, the format of the header depends on the type of device. For PCIe Endpoints, the format is as shown in Table 2.2.

Thus when the root complex communicates with PCIe Endpoints rather than simple PCI devices, it also reads these registers to enable communication with the devices. Important parameters such as the maximum payload size are read to enable successful PCIe transmission which is not

Figure 2.18: Layout of the PCI Express Configuration Space

| Bits [31-24] Bits [23-16]         | Bits [15-8]      | Bits [7-0]         | Byte Offset |  |  |  |  |

|-----------------------------------|------------------|--------------------|-------------|--|--|--|--|

| PCI Express Capabilities Register | Next Cap Pointer | PCI Express Cap ID | 0x00        |  |  |  |  |

| Device                            | e Capabilities   |                    | 0x04        |  |  |  |  |

| Device Status                     | Device           | Device Control     |             |  |  |  |  |

| Link                              | Capabilities     |                    | 0x1C        |  |  |  |  |

| Link Status                       | Link             | Control            | 0x10        |  |  |  |  |

Table 2.2: PCI Express Capability Structure of Endpoint Devices

required for PCI. The maximum payload size must be communicated between all devices to ensure that an unacceptable packet size is not sent. PCIe devices must ensure a maximum payload size of at least 128 bytes is provided so packets up to this size can be guaranteed to be accepted.

#### 2.6.4.2 PCI Enumeration and Configuration

The configuration of the devices is accomplished by making use of the standard format of the PCI Configuration Space. During start up, the configuration space of each device is attempted to be read to detect its presence.

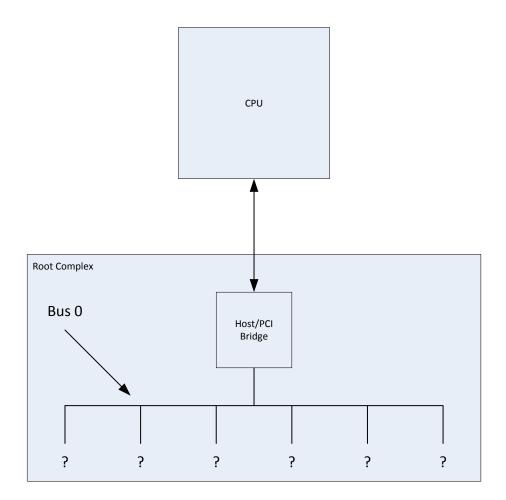

Initially only Bus 0 in the Root Complex has a bus number assigned. The header of each device is read to learn whether it exists or not. If it does and finds a bridge, it will search further down, then after reaching the bottom will traverse back up the tree. It performs a depth first search of all devices. On startup the system is unaware of the devices installed and thus the system looks as shown in Figure 2.19. There is no direct method for the BIOS or OS to determine which slots have peripherals or devices installed so the PCI buses need to be enumerated. In order to enumerate the peripheral devices, first the Device and Vendor ID registers are read. If nothing is read, the slots are taken as empty. The bus master performs an abort and returns all 1s in binary (0xFFFFFFF). This is an invalid Vendor ID/Device ID combination so the device driver can resolve that the device does not exist. When a successful read occurs, it then writes to the Base Address Registers (BARs) and reads back to investigate the memory locations on the Endpoint.

The lower bytes of a BAR indicate the type of memory device initialised. What these lower bytes indicate is shown in Table 2.3. For memory elements, BARs must be at least 128 bytes wide. BARs are 32 bits wide, so for 64 bit memory address, this takes up two adjacent bars.

The Base Address Register configuration is performed as follows. Once a device is discovered, the host writes 0xffffffff to the BAR and the BAR is

Figure 2.19: System Topology on Start-Up

| Bits | Description     | Values               |

|------|-----------------|----------------------|

|      | For all P       | CI BARs              |

| 0    | Region Type     | 0 = Memory           |

|      |                 | 1 = I/0 (deprecated) |

|      | For Memo        | ory BARs             |

| 2-1  |                 | 00 = any 32 bit      |

|      |                 | 10 = any 64 bit      |

| 3    | Prefetchable    | 0 = no               |

|      |                 | 1 = yes              |

| 6-4  | Reserved        |                      |

| 31-7 | Base Address    | 128-byte aligned     |

|      | For For 1/0 BAI | Rs (Deprecated)      |

| 1    | Reserved        |                      |

| 31-2 | Base Address    | 4-byte aligned       |

Table 2.3: Base Address Register Bit Assignments

then read back. For example, after 0xfffffff gets written to a BAR, say 0xfffff800 is read back. The zero bits give the assigned memory size where 16x16x8 = 2048 bytes. Once this memory space is known, the BIOS then programs the memory mapped and I/O port addresses the function will respond to into the BAR. These addresses are valid whilst the computer stays on. All settings are lost once power is removed and on next boot the procedure is repeated over again. This auto configuration on startup is how plug and play in implemented which means the user does not have to manually change settings to add hardware such as modifying DIP switches.

The enhanced PCIe configuration access mechanism utilises a flat memorymapped structure. The mapping from memory address space to PCI Express Configuration Space address is defined in Table 2.4.

#### 2.6. PCI EXPRESS ARCHITECTURE

| Memory Address     | PCI Express Configuration Space                          |

|--------------------|----------------------------------------------------------|

| A[(20 + n - 1):20] | Bus Number $1 \le n \le 8$                               |

| A [19:15]          | Device Number                                            |

| A [14:12]          | Function Number                                          |

| A [11:8]           | Extended Register Numbers                                |

| A [7:2]            | Register Number                                          |

| A [1:0]            | Along with size of access, used to generate Byte Enables |

Table 2.4: Enhanced Configuration Address Mapping

Figure 2.20: The standard Transaction Layer Packet structure

## 2.6.5 Packet Transactions

As described earlier, PCIe is a packet based technology. The encapsulation follows that shown in Figure 2.12. TLPs and DLLPs follow a standard packet structure where this and the transactions of these packets is detailed below.

#### 2.6.5.1 Transaction Layer Packet

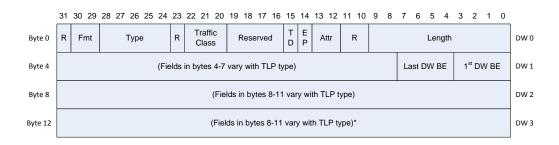

The most common packet is one sourced from the Transaction Layer. The header for such a packet meets the format shown in Figure 2.20. The header can be three or four DWs long. The headers of 32 bit memory packets are 3 DWs long whilst 64 bit memory packets are 4 DWs long.

The 'R' bits are the reserved bits which are set to '0' and do not do anything. 'Fmt' indicates the format of the packet. 'Type' indicates what type of the transaction it is such as a memory write transaction. 'TC' designates

#### CHAPTER 2. BACKGROUND

| Fmt[1:0] Field | TLP Format             |

|----------------|------------------------|

| 00             | 3 DW header, no data   |

| 01             | 4 DW header, no data   |

| 10             | 3 DW header, with data |

| 11             | 4 DW header, with data |

Table 2.5: Fmt Field Values

the traffic class of the packet. 'TD' describes the presence of a TLP digest and 'EP' indicates whether the TLP is poisoned. 'Attr' (or attributes) allows modification of the default handling of transactions such as the ordering and hardware coherency management.

From reading the 'Fmt' bits, the type of packet is read. This can be either a 3 DW header with no data ("00"), a 4 DW header with no data ("01"), a 3 DW header with data ("10") or a 4 DW header with data ("11"). If for example a memory read transaction is occurring, no payload will be appended as it will be expecting data in return. So the 'fmt' bits will be either "x0" or "x1" depending if 32 or 64 bit addressing is used.

The Fmt[1:0] field gives the size of the header and whether there is a data payload or not. The list of Fmt[1:0] codes is given in Table 2.5. The full list of Fmt and Type codes and their corresponding packet types are shown in Table 2.6.

Transactions are known as either "posted" or "non-posted". A posted transaction does not require a response. For example, a Memory Write request is considered a posted transaction as the data gets sent to a particular location, and no response is required to complete the transaction. A non-posted transaction is one which requires a response. For example, a Memory Read transaction is classified as a non-posted transaction as is starts a transaction and requires a completion packet to complete this transaction.

Although Memory Write requests do not require completion packets, Configuration Writes do require a completion packet. This is simply a

## 2.6. PCI EXPRESS ARCHITECTURE

| TLP Type                                       | Fmt[1:0] | Type[4:0] |

|------------------------------------------------|----------|-----------|

|                                                | Field    | Field     |

| Memory Read Request (MRd)                      | 00       | 0 0000    |

|                                                | 01       |           |

| Memory Read Request-Locked (MRdLk)             | 00       | 0 0001    |

|                                                | 01       |           |

| Memory Write Request (MWr)                     | 10       | 0 0000    |

|                                                | 11       |           |

| I/O Read Request (IORd)                        | 00       | 0 0010    |

| I/O Write Request (IOWr)                       | 10       | 0 0010    |

| Configuration Read Type 0 (CfgRd0)             | 00       | 0 0100    |

| Configuration Write Type 0 (CfgWr0)            | 10       | 0 0100    |

| Configuration Read Type 1 (CfgRd1)             | 00       | 0 0101    |

| Configuration Write Type 1 (CfgWr1)            | 10       | 0 0101    |

| Message Request (Msg)                          | 01       | 1 Orrr    |

| Message Request with Data (MsgD)               | 11       | 1 Orrr    |

| Completion without Data (Cpl)                  | 00       | 0 1010    |

| Completion with Data (CplD)                    | 10       | 0 1010    |

| Completion for Locked Memory Read without Data | 00       | 0 1011    |

| (CplLk)                                        |          |           |

| Completion for Locked Memory Read (CplDLk)     | 10       | 0 1011    |

| Completion for Locked Memory Read (CpIDLk)     | 10       | 0 1011    |

Table 2.6: Description of TLP Fmt and Type codes

Figure 2.21: Memory Write Packet

completion with no data to confirm that it successfully completed as this is paramount to the system working successfully. For example, when programming the BARs, confirmation is needed that it has been written successfully before a read is signalled.

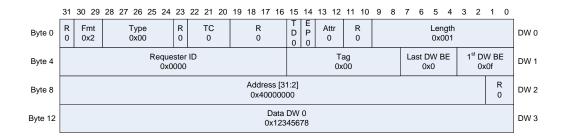

An example of a posted Memory Write packet is shown in Figure 2.21. As can be seen, the fmt and type fields correspond to a 32 bit memory write request. This packet is of length 1, so contains one DW of data. Here, the address to be sent to is 0x10000000. However, the lower two bits of the address are reserved. Hence this is equivalent to a 30 bit hex value of 0x40000000. DW4 of this packet is the data to be written to the target. No completion is required to be returned for this transaction. The data of PCIe packets is Big Endian. However, x86 processors are little endian. Thus data of 0x12345678 is interpreted as 0x78563412 on an x86 processor.

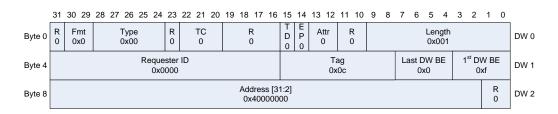

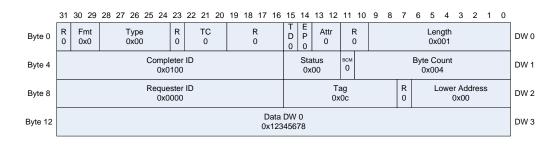

An example of a non-posted Memory Read packet is shown in Figure 2.22. As can be seen, the fmt and type fields correspond to a memory read request. The length of the packet is 1 so a completion with 1DW of data is expected. Again the lower two address bits are reserved so the address gets multiplied by four to get the actual address. This packet then gets passed along to the target. The target then retrieves the data and sends a completion packet back with the desired data. This packet is shown in Figure 2.23.

#### 2.6. PCI EXPRESS ARCHITECTURE

#### Figure 2.22: Memory Read Request Packet

Figure 2.23: Memory Read Completion Packet

#### 2.6.5.2 Data Link Layer Packet

Memory, IO, messages, configuration and completion packets are formed in the Transaction Layer. However there are also packets formed in the Data Link Layer which deal with the upkeep of the link. The standard format of a Data Link Layer sourced packet is shown in Figure 2.24. The Data Link Layer packets comprise of four different types: positive acknowledgement (Ack), negative acknowledgement (Nak), flow control (FC) and power management (PM). The sequence number adds 2 bytes of overhead where 12 bits comprises the actual sequence number and four bits are reserved. The DLLP Type field indicates whether it is an Ack, Nak, Power Management or Flow Control packet. These are shown in Table 2.7.

Ack or Nak packets are initiated to let the sending device know that a Memory Write or Memory Read request was successful or not. If it was not successful, the packet gets resent.

|        | 31 30 29 | 28 2   | 27 2 | 6 25 | 24    | 23   | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14    | 13   | 12  | 11   | 10    | 9    | 8   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|----------|--------|------|------|-------|------|----|----|----|----|----|----|----|----|-------|------|-----|------|-------|------|-----|---|---|---|---|---|---|---|---|

| Byte 0 | D        | ILLP T | Гуре |      |       | R    |    |    |    |    |    |    |    | (1 | Field | ls V | ary | With | 1 DLI | _P T | ype | ) |   |   |   |   |   |   |   |

| Byte 4 |          |        |      | 1    | I6 Bi | t CR | с  |    |    |    |    |    |    |    |       |      |     |      |       |      |     |   |   |   |   |   |   |   |   |

Figure 2.24: The standard Data Link Layer Packet structure

| Encodings           | DLLP Type                                      |

|---------------------|------------------------------------------------|

| 0000 0000           | Ack                                            |

| 0001 0000           | Nak                                            |

| 0010 0000           | PM_Enter_L1                                    |

| 0010 0001           | PM_Enter_L23                                   |

| 0010 0011           | PM_Active_State_Request_L1                     |

| 0010 0100           | PM_Request_Ack                                 |

| 0011 0000           | Vendor Specific - Not used in normal operation |

| $0100 0v_2v_1v_0$   | InitFC1-P (v[2:0] specifies Virtual Channel)   |

| $0101 0v_2v_1v_0$   | InitFC1-NP                                     |

| $0110 0v_2v_1v_0$   | InitFC1-Cpl                                    |

| $1100 0v_2v_1v_0$   | InitFC2-P                                      |

| $1101 0v_2v_1v_0$   | InitFC2-NP                                     |

| $1110 0v_2v_1v_0$   | InitFC2-Cpl                                    |

| $1000 0v_2v_1v_0$   | UpdateFC-P                                     |

| $1001 \ 0v_2v_1v_0$ | UpdateFC-NP                                    |

| $1010 0v_2v_1v_0$   | UpdateFC-Cpl                                   |

| All other encodings | Reserved                                       |

Table 2.7: Description of DLLP Type codes

2.7. FPGA

## 2.7 FPGA

Many digital designs are moving from using dedicated digital logic to Field Programmable Gate Array (FPGA) based systems. FPGAs are a flexible alternative to an application-specific integrated circuit (ASIC). A typical FPGA contains a number of *logic blocks* and reconfigurable interconnects wiring the logic blocks together. When combined, these logic blocks can perform complex tasks or be as simple as a basic logic gate. FPGAs typically contain other elements such as memory. Almost all of the peripheral devices designed by Magritek make use of an FPGA to control the system. The PXIe Peripheral Module was also designed using an FPGA as a central element.

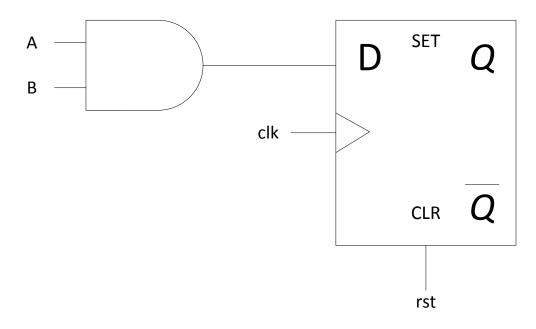

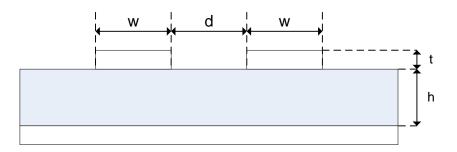

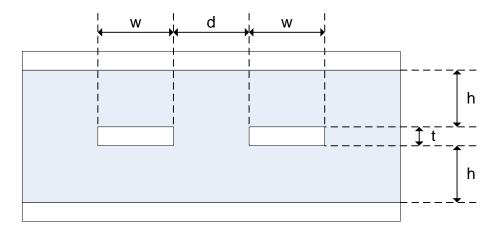

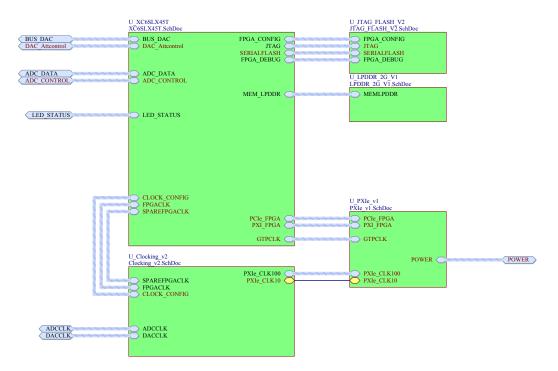

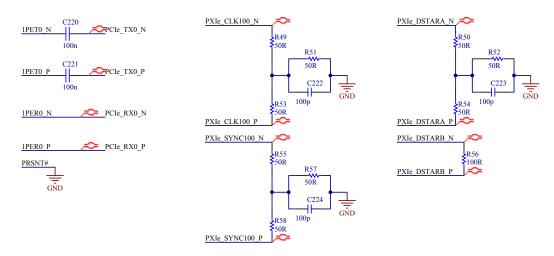

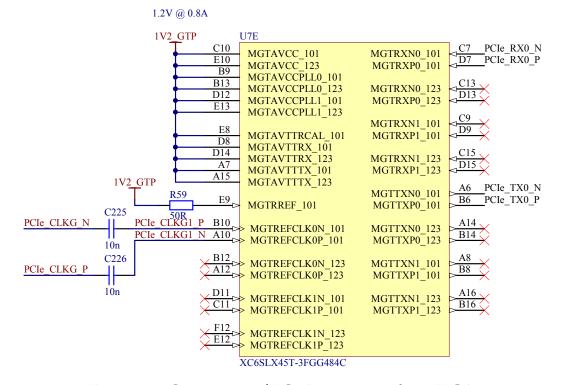

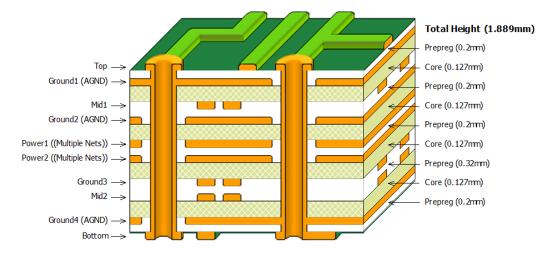

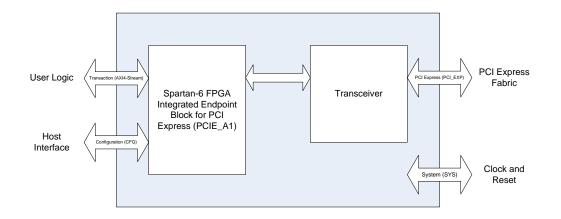

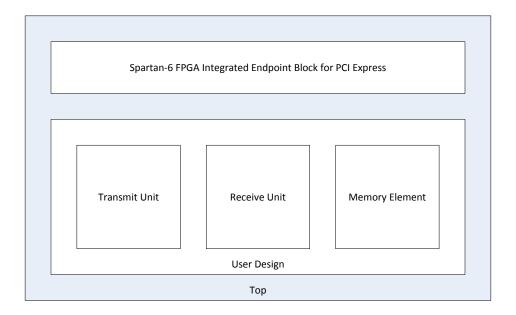

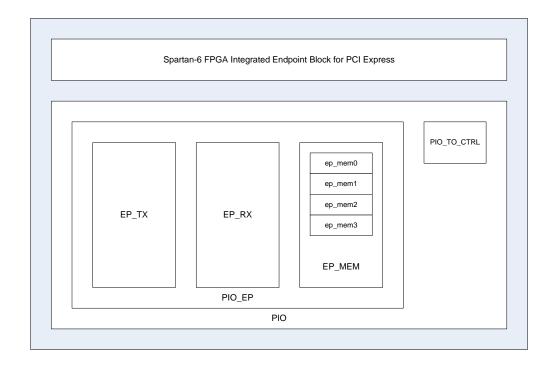

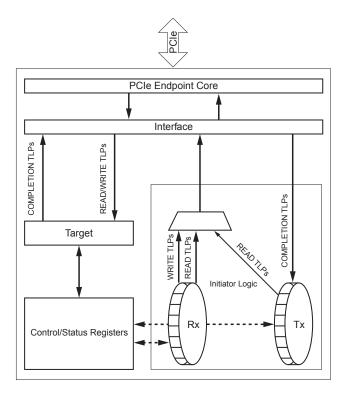

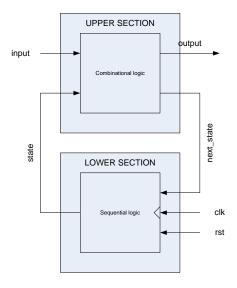

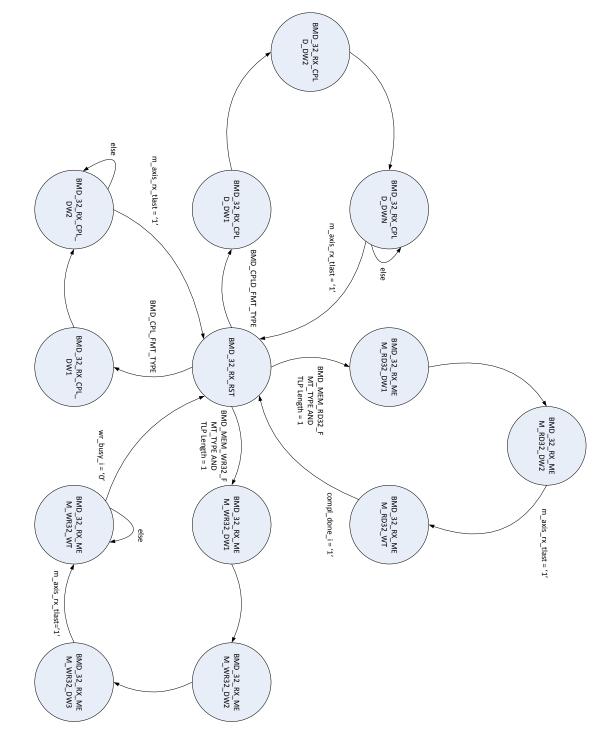

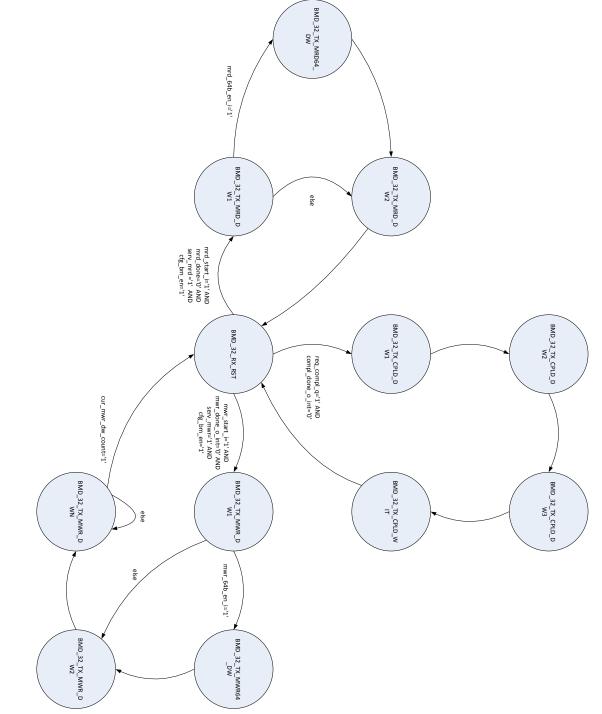

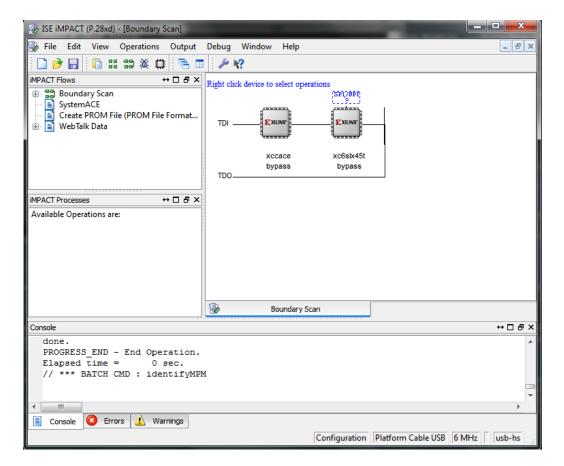

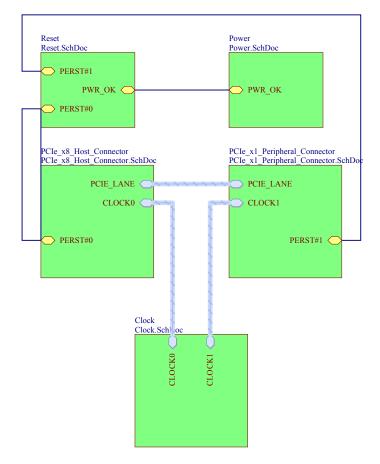

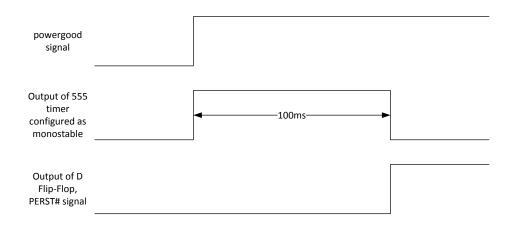

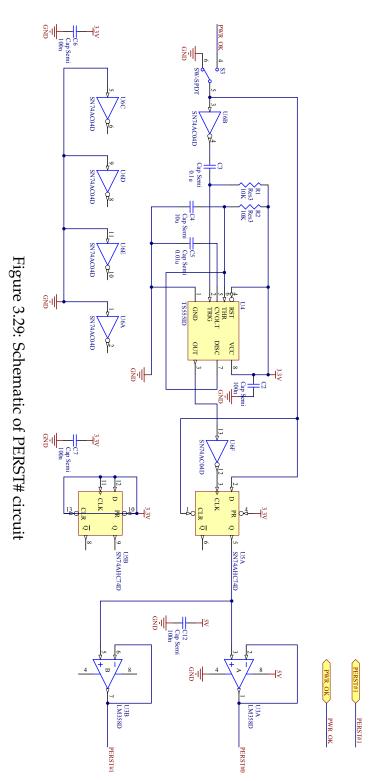

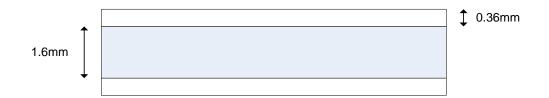

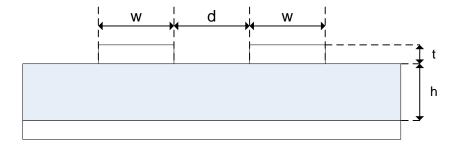

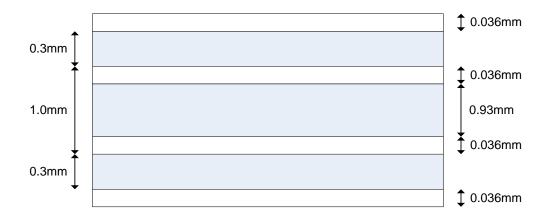

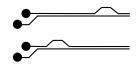

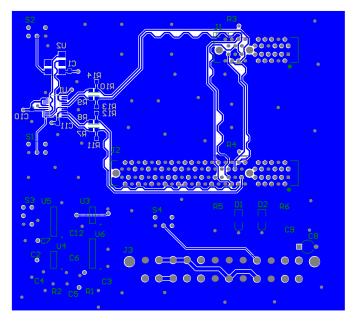

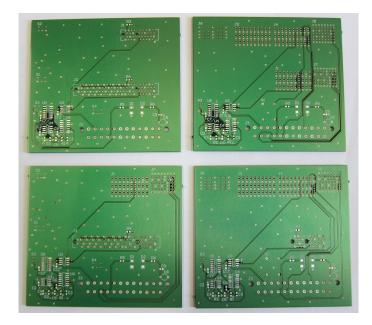

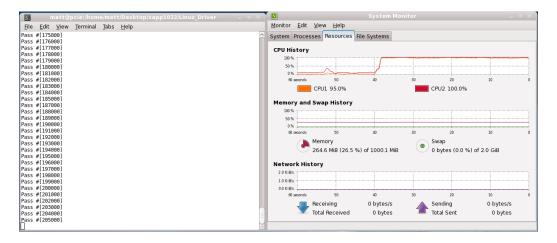

FPGA devices provide a lot of flexibility to the designer and allow for rapid prototyping of digital designs. FPGAs are traditionally configured using a Hardware Description Language (HDL) which describes the circuits operation and organisation. HDLs can furthermore be used to verify operation via simulation. The two main forms of HDL are Very-High-Speed Integrated Circuit HDL (VHDL) and Verilog. VHDL, based off ADA, is verbose and employs strong typing, whereas Verilog is similar to C in syntax but employs weak typing [21].