### On the Use of Model Checking for the Bounded and Unbounded Verification of Nonblocking Concurrent Data Structures

by

David Friggens

A thesis submitted to Victoria University of Wellington in fulfilment of the requirements for the degree of Doctor of Philosophy in Logic and Computation.

> Victoria University of Wellington 2013

This work is licensed under the Creative Commons Attribution 3.0 New Zealand License. To view a copy of this license, visit http://creativecommons.org/licenses/by/3.0/nz/ or send a letter to Creative Commons, 444 Castro Street, Suite 900, Mountain View, California, 94041, USA.

#### Abstract

Concurrent data structure algorithms have traditionally been designed using locks to regulate the behaviour of interacting threads, thus restricting access to parts of the shared memory to only one thread at a time. Since locks can lead to issues of performance and scalability, there has been interest in designing so-called nonblocking algorithms that do not use locks. However, designing and reasoning about concurrent systems is difficult, and is even more so for nonblocking systems, as evidenced by the number of incorrect algorithms in the literature.

This thesis explores how the technique of model checking can aid the testing and verification of nonblocking data structure algorithms. Model checking is an automated verification method for *finite state* systems, and is able to produce counterexamples when verification fails. For verification, concurrent data structures are considered to be *infinite state systems*, as there is no bound on the number of interacting threads, the number of elements in the data structure, nor the number of possible distinct data values. Thus, in order to analyse concurrent data structures with model checking, we must either place finite bounds upon them, or employ an abstraction technique that will construct a finite system with the same properties.

First, we discuss how nonblocking data structures can be best represented for model checking, and how to specify the properties we are interested in verifying. These properties are the safety property linearisability, and the progress properties wait-freedom, lock-freedom and obstructionfreedom.

Second, we investigate using model checking for exhaustive testing, by verifying bounded (and hence finite state) instances of nonblocking data structures, parameterised by the number of threads, the number of distinct data values, and the size of storage memory (e.g. array length, or maximum number of linked list nodes). It is widely held, based on anecdotal evidence, that most bugs occur in small instances. We investigate the smallest bounds needed to falsify a number of incorrect algorithms, which supports this hypothesis. We also investigate verifying a number of correct algorithms for a range of bounds. If an algorithm can be verified for bounds significantly higher than the minimum bounds needed for falsification, then we argue it provides a high degree of confidence in the general correctness of the algorithm. However, with the available hardware we were not able to verify any of the algorithms to high enough bounds to claim such confidence.

Third, we investigate using model checking to verify nonblocking data structures by employing the technique of canonical abstraction to construct finite state representations of the unbounded algorithms. Canonical abstraction represents abstract states as 3-valued logical structures, and allows the initial coarse abstraction to be refined as necessary by adding derived predicates. We introduce several novel derived predicates and show how these allow linearisability to be verified for linked list based nonblocking stack and queue algorithms. This is achieved within the standard canonical abstraction framework, in contrast to recent approaches that have added extra abstraction techniques on top to achieve the same goal.

The finite state systems we construct using canonical abstraction are still relatively large, being exponential in the number of distinct abstract thread objects. We present an alternative application of canonical abstraction, which more coarsely collapses all threads in a state to be represented by a single abstract thread object. In addition, we define further novel derived predicates, and show that these allow linearisability to be verified for the same stack and queue algorithms far more efficiently.

### Acknowledgements

I owe many thanks to my principal supervisor, Lindsay Groves. He suggested this area of research, and has provided much guidance, advice and proof reading. My initial secondary supervisor, Ray Nickson, also provided much appreciated guidance and advice.

Thanks to my examiners — Mooly Sagiv, Steve Reeves and David Pearce — for their careful reading, kind words, and helpful suggestions.

Financially, I have been supported by a VUW Postgraduate Scholarship and a VUW PhD Submission Scholarship. A grant from Sun Microsystems provided some travel funds, notably to attend the 17th International School for Computer Science Researchers in Lipari, Italy.

This thesis was almost entitled "Model Checking for Godot", so a special thank you is due to Lindsay and all the VUW administrators who have had to employ much patience. I hope you agree it was worth the wait.

I am grateful for the hospitality and understanding of the Department of Computer Science and Library at the University of Waikato, including the use of the "symphony" computing cluster.

Thanks to my parents for everything. Especially for not asking any questions about my progress in the last two years — it was hard, but it helped.

Finally, I can never thank Olivia enough for her love, encouragement and support. Ultimately, this thesis only exists because of the sacrifices she has made. Our co-publications, produced during the writing of the thesis, are extremely well cited due to her input.

ACKNOWLEDGEMENTS

### Contents

| Ac | knov               | ledgements                                               | iii           |

|----|--------------------|----------------------------------------------------------|---------------|

| Co | onten              | 5                                                        | v             |

| Li | st of ]            | igures                                                   | xiii          |

| Li | st of '            | ables                                                    | xvii          |

| 1  | <b>Intr</b><br>1.1 | <b>duction</b><br>Nonblocking Concurrency                | <b>1</b><br>1 |

|    | 1.1                | Model Checking                                           | -             |

|    | 1.3                | Bounded Verification                                     |               |

|    | 1.4                | Unbounded Verification                                   |               |

|    | 1.5                | Outline                                                  | 5             |

| Ι  | Bac                | kground                                                  | 7             |

| 2  | Non                | plocking Data Structures                                 | 9             |

|    | 2.1                | Concurrent Data Structures                               | 9             |

|    | 2.2                | Linearisability                                          | 11            |

|    | 2.3                | Mutual Exclusion                                         | 13            |

|    | 2.4                | Nonblocking Progress Properties                          |               |

|    |                    | 2.4.1 Wait-freedom                                       | 15            |

|    |                    | 2.4.2 Lock-freedom                                       | 15            |

|    |                    | 2.4.3 Obstruction-freedom                                | 16            |

|    | 2.5                | Nonblocking Synchronization                              |               |

|    |                    | 2.5.1Compare-and-Swap2.5.2Load-Linked, Store-Conditional |               |

|   |     | 2.5.3   | ABA Problem                                      |

|---|-----|---------|--------------------------------------------------|

|   |     | 2.5.4   | Memory Management                                |

|   | 2.6 | Algori  | ithms                                            |

|   |     | 2.6.1   | Lock-free Stack                                  |

|   |     | 2.6.2   | Lock-free Unbounded Queue                        |

| 3 | Мос | del Che | cking 27                                         |

|   | 3.1 |         | ns                                               |

|   | 3.2 | 5       | ications                                         |

|   |     | 3.2.1   | CTL*                                             |

|   |     | 3.2.2   | LTL                                              |

|   |     | 3.2.3   | CTL                                              |

|   |     | 3.2.4   | Linear- versus Branching-time                    |

|   | 3.3 | Mode    | Checking Paradigms                               |

|   |     | 3.3.1   | Explicit State Model Checking                    |

|   |     | 3.3.2   | BDD-Based Symbolic Model Checking                |

|   |     | 3.3.3   | Bounded Model Checking                           |

|   | 3.4 |         | ng the State Explosion Problem                   |

|   |     | 3.4.1   | Bitstate hashing                                 |

|   |     | 3.4.2   | Partial order reduction                          |

|   |     | 3.4.3   | Slicing                                          |

|   |     | 3.4.4   | Symmetry reduction                               |

|   | 3.5 | Abstra  | action                                           |

|   |     | 3.5.1   | Constructing Abstract Models                     |

|   | 3.6 | Tools   |                                                  |

|   |     | 3.6.1   | Spin                                             |

|   |     | 3.6.2   | SAL                                              |

|   |     | 3.6.3   | TVLA/3VMC 47                                     |

| 4 | Can | onical  | Abstraction 49                                   |

| T | 4.1 |         | nical Abstraction                                |

|   | 4.1 | 4.1.1   | States as Logical Structures                     |

|   |     | 4.1.1   | 8                                                |

|   |     | 4.1.2   | Embeddings52Canonical Abstraction54              |

|   |     | 4.1.3   |                                                  |

|   |     | 4.1.3   | 1                                                |

|   |     |         | Syntax         55           Semantics         56 |

|   |     |         |                                                  |

|   | 4 0 | Dofini  | 0                                                |

|   | 4.2 | Kenni   | ng Abstractions                                  |

|    |     | 4.2.1     | Integrity Rules                        | 58 |

|----|-----|-----------|----------------------------------------|----|

|    |     | 4.2.2     | Instrumentation Predicates             | 59 |

|    | 4.3 | Abstra    | act Transitions                        | 65 |

|    |     | 4.3.1     | Focus Operation                        | 66 |

|    |     | 4.3.2     | Coerce Operation                       | 67 |

|    |     |           | Compatibility constraints              | 69 |

|    |     |           | Coerce algorithm                       | 70 |

|    |     | 4.3.3     | Update                                 | 70 |

|    |     |           | New objects                            | 71 |

|    |     | 4.3.4     | Example                                | 71 |

|    |     |           | Initial State                          | 72 |

|    |     |           | Focus                                  | 73 |

|    |     |           | Coerce                                 | 74 |

|    |     |           | Update                                 | 75 |

|    |     |           | Coerce                                 | 76 |

|    |     |           | Blur                                   | 76 |

|    |     | 4.3.5     | Computing the Best Abstract Transition | 76 |

|    | 4.4 | Concu     | Irrent Systems                         | 76 |

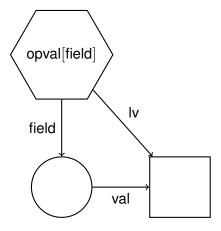

|    |     | 4.4.1     | States                                 | 77 |

|    |     | 4.4.2     | Transitions                            | 77 |

|    |     |           | Unschedule                             | 78 |

|    |     |           | Schedule                               | 79 |

|    | 4.5 | Impro     | vements                                | 79 |

|    |     | 4.5.1     | Summary Predicate                      | 79 |

|    |     | 4.5.2     | Partially Disjunctive Analysis         | 80 |

|    |     | 4.5.3     | Coerce                                 | 80 |

|    |     | 4.5.4     | Instrumentation Predicate Updates      | 81 |

|    |     | 4.5.5     | Graph Decomposition                    | 81 |

|    |     |           |                                        |    |

| Π  | М   | - d - 11: | na and Testing                         | 07 |

| 11 | IVI | odem      | ng and Testing                         | 83 |

| 5  | Mod | lel Che   | cking Nonblocking Algorithms           | 85 |

|    | 5.1 |           | lling Data Structures                  | 85 |

|    |     | 5.1.1     | Transition Systems                     | 86 |

|    |     | 5.1.2     | Creating Finite Systems                | 87 |

|    |     |           | Bounded Parameters                     | 87 |

| • • • • • • |                             | - |

|-------------|-----------------------------|---|

|             | Bounded Parameters          | 7 |

|             | Unbounded Abstract Models   | 7 |

| 5.1.3       | Manual Statespace Reduction | 8 |

|   |     |        | Resetting Unused Values            |

|---|-----|--------|------------------------------------|

|   |     |        | Reducing Interleaving              |

|   | 5.2 | Specif | ying Linearisability               |

|   |     | 5.2.1  | Concurrent Specifications          |

|   |     | 5.2.2  | Linearisation Points               |

|   |     | 5.2.3  | Simulation                         |

|   |     |        | Use of Simulation                  |

|   |     | 5.2.4  | Direct Trace Inclusion             |

|   |     | 5.2.5  | Future Nondeterminism              |

|   |     |        | Backwards analysis                 |

|   |     |        | Prophecy variables                 |

|   |     |        | Multiple Linearisation Points      |

|   |     | 5.2.6  | Merging the Specification          |

|   | 5.3 | Specif | Tying Nonblocking Properties       |

|   |     | 5.3.1  | Wait-freedom                       |

|   |     | 5.3.2  | Lock-freedom                       |

|   |     |        | Thread-level view                  |

|   |     | 5.3.3  | Obstruction-freedom                |

|   |     | 5.3.4  | Related Work                       |

| 6 | Bou | nded V | /erification 117                   |

|   | 6.1 | Check  | king Linearisability               |

|   |     | 6.1.1  | Example                            |

|   |     | 6.1.2  | Minimal Counterexamples            |

|   |     | 6.1.3  | Confidence in Bounded Verification |

|   |     | 6.1.4  | Verification Limits                |

|   |     |        | Spin Reduction                     |

|   |     |        | Symmetry Reduction                 |

|   | 6.2 | Check  | king Nonblocking Properties        |

|   |     | 6.2.1  | Example                            |

|   |     | 6.2.2  | Minimal Counterexamples            |

|   |     | 6.2.3  | Confidence in Bounded Verification |

|   |     | 6.2.4  | Verification Limits                |

|   | 6.3 | Relate | ed Work                            |

|   | 6.4 | Concl  | usion                              |

viii

| II | [ V | erifica | ation                                  | 137 |

|----|-----|---------|----------------------------------------|-----|

| 7  | Can | onical  | Abstraction for Linearisability        | 139 |

|    | 7.1 |         | Stack Model                            | 141 |

|    | 7.2 |         | -Valued Model                          |     |

|    |     | 7.2.1   | Core Predicates                        | 145 |

|    |     | 7.2.2   | Integrity Rules                        |     |

|    |     | 7.2.3   | Instrumentation Predicates             |     |

|    |     |         | Reachability and circularity           |     |

|    |     |         | Has-a-field.                           |     |

|    |     |         | Referenced-by-field                    | 147 |

|    |     |         | Shared                                 |     |

|    | 7.3 | Preser  | rving Linearisability Information      | 148 |

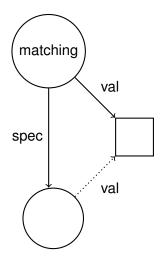

|    |     | 7.3.1   | Matching Values                        |     |

|    |     | 7.3.2   | Ordered Values                         | 154 |

|    |     | 7.3.3   | Hanging Head                           | 156 |

|    | 7.4 | (Un)b   | ounded Threads                         |     |

|    |     | 7.4.1   | Bounded Threads                        | 161 |

|    |     | 7.4.2   | Thread Field Properties                | 162 |

|    |     |         | Snapshots                              | 162 |

|    |     |         | Data Values                            | 164 |

|    | 7.5 | Initial | State                                  | 167 |

|    | 7.6 | Addit   | ional Compatibility Constraints        | 169 |

|    |     | 7.6.1   | Reachability Predicates                | 169 |

|    |     | 7.6.2   | Geometric Predicates                   | 177 |

|    | 7.7 | Stack   | Results                                | 179 |

|    | 7.8 | Stack   | Variations                             | 181 |

|    |     | 7.8.1   | TVLA Changes                           | 181 |

|    |     |         | Isomorphic State Comparison            |     |

|    |     |         | TVLA 2                                 |     |

|    |     | 7.8.2   | Definitions                            | 183 |

|    |     |         | Unnecessary Instrumentation Predicates | 183 |

|    |     |         | Pure Initial State                     | 184 |

|    |     |         | Named Threads                          | 185 |

|    |     |         | Thread Bounding Constraint             | 185 |

|    |     | 7.8.3   | Full Interleaving                      | 186 |

|    | 7.9 | Queu    | e Models                               |     |

|    |     | 7.9.1   | Three-Valued Models                    | 188 |

|    |     |         | Core Predicates                        | 188 |

|        |         | Instrumentation Predicates          | 193 |

|--------|---------|-------------------------------------|-----|

|        | 7.9.2   | Results                             | 194 |

| 7.10   | Related | d Work                              | 195 |

| 7.11   | Conclu  | asion                               | 196 |

| 8 Coll | apsing  | Threads Safely with Soft Invariants | 199 |

| 8.1    | Overvi  | iew                                 | 200 |

|        | 8.1.1   | Instrumentation Predicates          | 200 |

|        | 8.1.2   | Selection of Predicates             | 202 |

|        | 8.1.3   | Compatibility Constraints           | 205 |

| 8.2    | Stack N | Models                              | 206 |

|        | 8.2.1   | Changes to the Model                | 206 |

|        |         | Collapse                            | 206 |

|        |         | Null Equivalence                    | 207 |

|        | 8.2.2   | Soft Invariants                     | 209 |

|        |         | Interleaved Locations               | 209 |

|        |         | Non-interleaved Locations           | 213 |

|        | 8.2.3   | Results                             | 213 |

|        | 8.2.4   | Full Interleaving                   | 213 |

|        |         | Soft Invariants                     | 214 |

|        |         | Results                             | 214 |

|        | 8.2.5   | Extra Predicates                    | 216 |

| 8.3    | Queue   | Models                              | 217 |

|        | 8.3.1   | Changes to the model                | 218 |

|        |         | Full interleaving                   | 218 |

|        |         | Ordered snapshots                   | 218 |

|        | 8.3.2   | Soft Invariants                     | 224 |

|        |         | Enqueue                             | 228 |

|        |         | Simplified Dequeue                  | 228 |

|        |         | Original Dequeue                    |     |

|        |         | Restricted Interleaving             | 229 |

|        | 8.3.3   | Results                             | 229 |

| 8.4    | Conclu  | asion                               | 231 |

|        |         |                                     |     |

|        |         |                                     |     |

# 9 Conclusion 235 9.1 Bounded Verification 235

|   |      | 9.1.1         | Future Research                                 |     |

|---|------|---------------|-------------------------------------------------|-----|

|   | 9.2  | Unboı         | unded Verification                              | 237 |

|   |      | 9.2.1         | Future Research                                 | 238 |

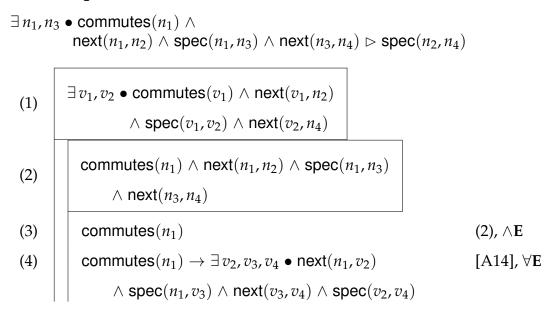

| Α | Proc | ofs of C      | Canonical Abstraction Compatibility Constraints | 239 |

|   |      |               | nptions                                         | 239 |

|   |      |               | variants                                        |     |

|   |      | A.2.1         | Single predicate                                |     |

|   |      | A.2.2         | Conditional property                            |     |

|   | A.3  |               | · · · · · · · · · · · · · · · · · · ·           |     |

|   |      | A.3.1         |                                                 |     |

|   |      | A.3.2         | Same 1                                          |     |

|   |      | A.3.3         | Same 2                                          |     |

|   |      | A.3.4         | Ordered                                         |     |

|   | A.4  | Geom          | etric                                           |     |

|   |      | A.4.1         | Triangle 1                                      |     |

|   |      | A.4.2         | Triangle 2                                      |     |

|   |      | A.4.3         | Square 1                                        |     |

|   |      | A.4.4         | Square 2                                        |     |

|   |      | A.4.5         | Square 3                                        |     |

|   | A.5  |               | ability                                         |     |

|   | 11.0 | A.5.1         | No self loop                                    |     |

|   |      | A.5.2         | No loop back                                    |     |

|   |      | A.5.3         | No loop to head                                 |     |

|   |      | A.5.4         | Unreachable                                     |     |

|   |      | A.5.5         | Chain                                           |     |

|   |      | <b>A</b> .J.J |                                                 | 200 |

|   |      |               |                                                 |     |

#### Bibliography

CONTENTS

xii

# **List of Figures**

| Basic counter implementation                              | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

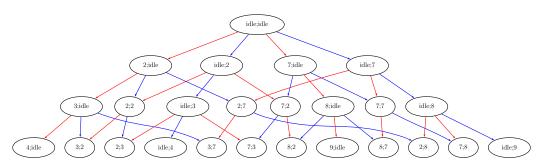

| Initial part of the counter execution graph               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

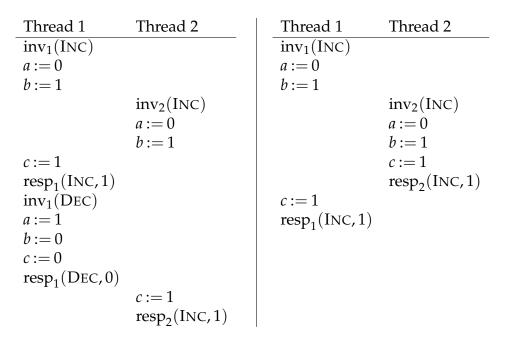

| Two counter executions                                    | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Counter algorithm with a lock                             | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pseudocode for Compare-and-Swap                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Nonblocking counter increment operations                  | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (a) Using CAS                                             | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A lock-free stack algorithm                               | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A lock-free linked list based queue                       | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (a) Initialisation and enqueue operation                  | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (b) Original dequeue operation                            | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (c) Simplified dequeue operation                          | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

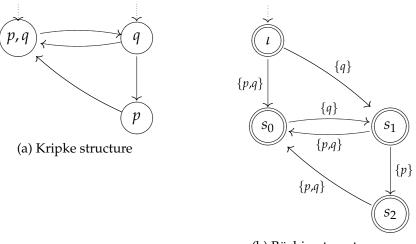

| Example Kripke structure                                  | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                           | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

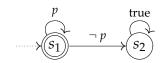

|                                                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| (b) Büchi automaton                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A Büchi automaton for $\mathbf{AG}p$                      | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

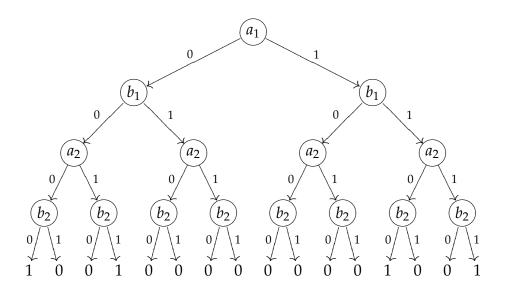

| A binary decision tree for a two-bit comparator           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OBDDs for a two-bit comparator                            | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

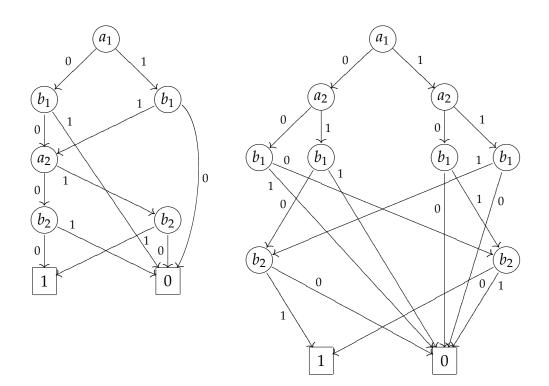

| Independent transition execution                          | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

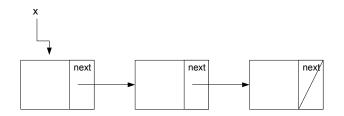

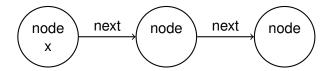

| A list of length three                                    | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                           | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

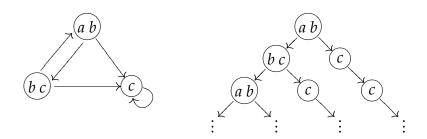

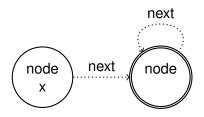

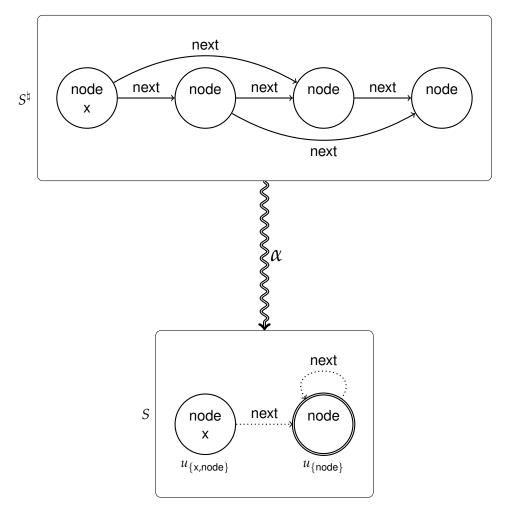

|                                                           | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                           | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

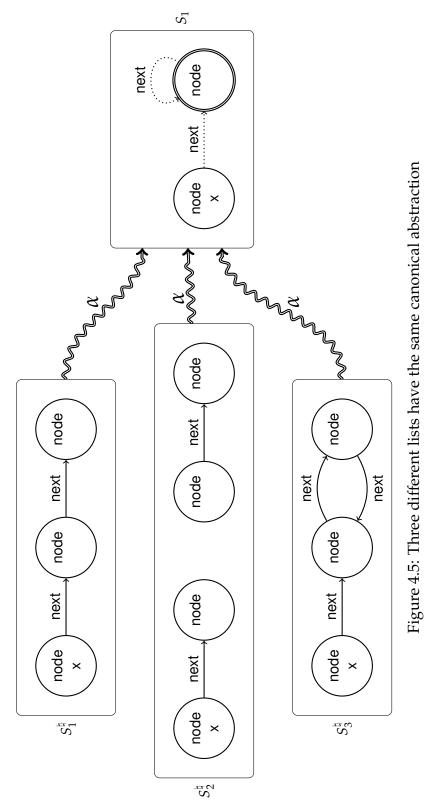

| Three different lists have the same canonical abstraction | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                           | Initial part of the counter execution graphTwo counter executionsCounter algorithm with a lockPseudocode for Compare-and-SwapNonblocking counter increment operations(a) Using CAS(b) Using LL/SCA lock-free stack algorithmA lock-free linked list based queue(a) Initialisation and enqueue operation(b) Original dequeue operation(c) Simplified dequeue operationExample Kripke structureA Kripke structure and its computation treeTwo equivalent system representations(a) Kripke structure(b) Büchi automaton for $AGp$ A binary decision tree for a two-bit comparatorOBDDs for a two-bit comparatorIndependent transition executionA list of length threeGraph of concrete configurationGraph of abstract configurationCanonical abstraction of a non-functional field |

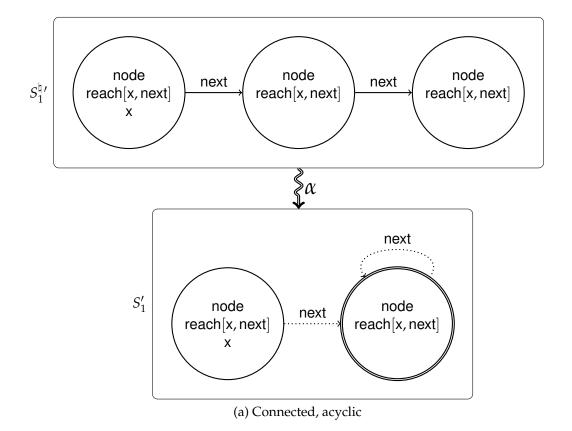

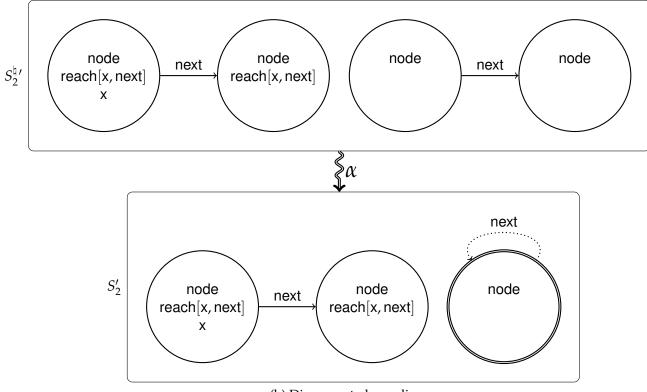

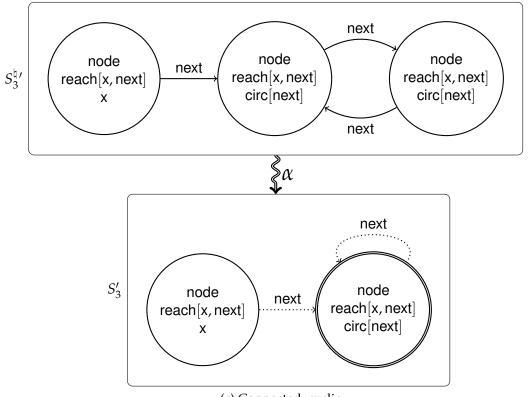

| 4.6 | Using instrumentation predicates to distinguish three dif-                                                                                                   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | ferent list structures                                                                                                                                       |

|     | (a) Connected, acyclic $\dots \dots \dots$                   |

|     | (b) Disconnected, acyclic $\dots \dots \dots$                |

| 4 🗖 | (c) Connected, cyclic $\ldots \ldots \ldots$ |

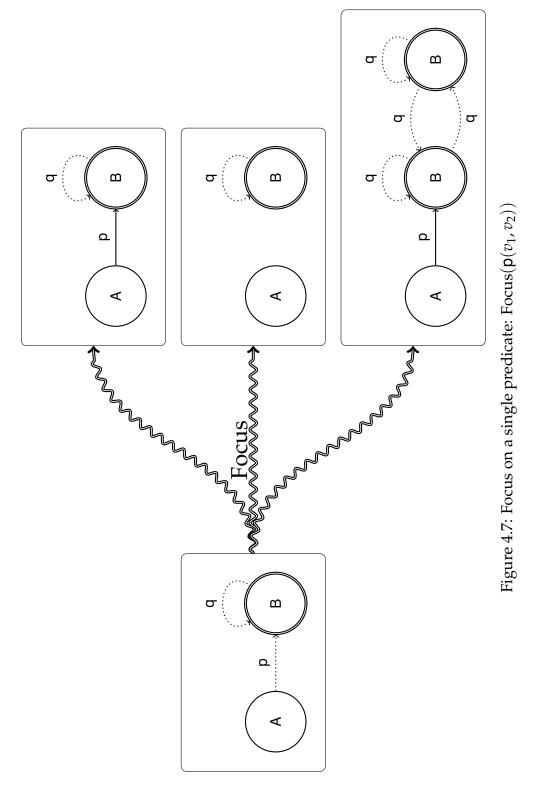

| 4.7 | Focus on a single predicate: Focus $(p(v_1, v_2))$                                                                                                           |

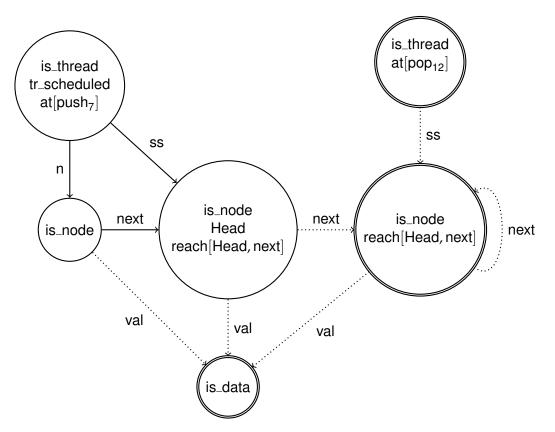

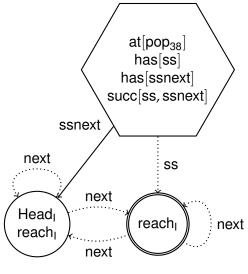

| 4.8 | Graph of a stack algorithm state with concurrent threads 78                                                                                                  |

| 5.1 | A lock-free stack algorithm with merged transitions 89                                                                                                       |

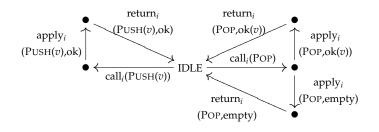

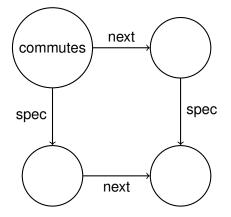

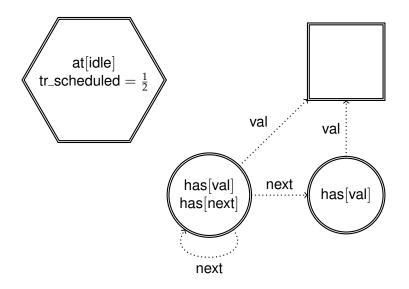

| 5.2 | Diagram of thread $i$ in the concurrent stack specification $\dots$ 91                                                                                       |

| 5.3 | Operations of thread $i$ in the concurrent stack specification . 91                                                                                          |

| 5.4 | A lock-free linked list based queue with prophecy variables 101                                                                                              |

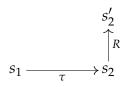

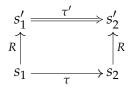

| 5.5 | Diagrams of Dequeue operation of Thread <i>i</i> of a concurrent                                                                                             |

|     | stack specification                                                                                                                                          |

|     | (a) Original                                                                                                                                                 |

|     | (b) With multiple linearisation points                                                                                                                       |

| 5.6 | A lock-free stack algorithm with merged specification 105                                                                                                    |

| 5.7 | A lock-free queue algorithm with merged specification 107                                                                                                    |

|     | (a) Enqueue operation                                                                                                                                        |

|     | (b) Original dequeue operation                                                                                                                               |

|     | (c) Simplified dequeue operation                                                                                                                             |

| 6.1 | Simplified execution of stack showing ABA error counter-                                                                                                     |

|     | example                                                                                                                                                      |

| 6.2 | Promela never claim for LTL formula WF-1                                                                                                                     |

| 6.3 | Simplified execution of stack showing wait-freedom coun-                                                                                                     |

|     | terexample                                                                                                                                                   |

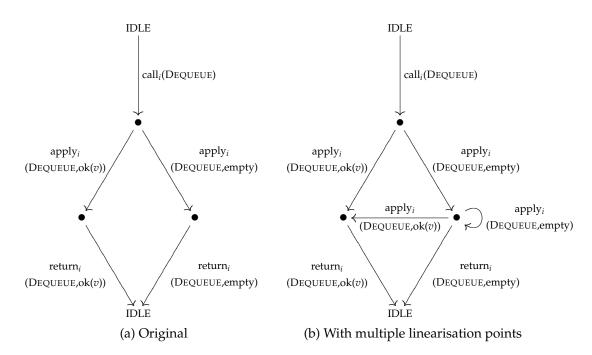

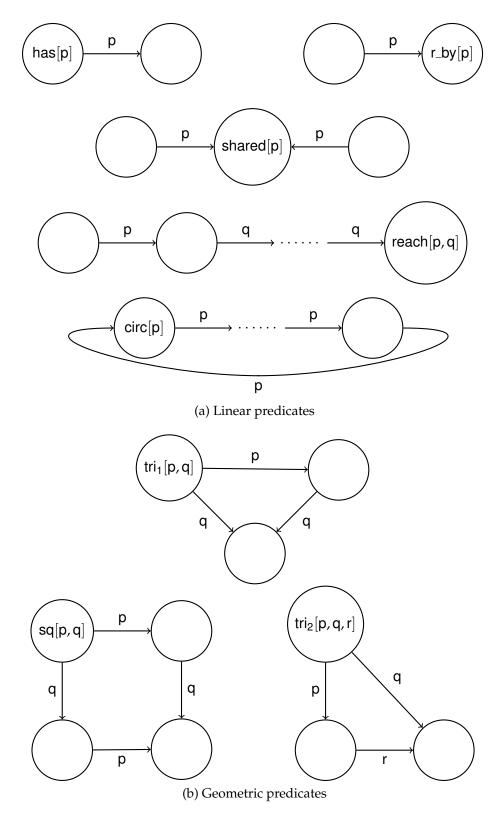

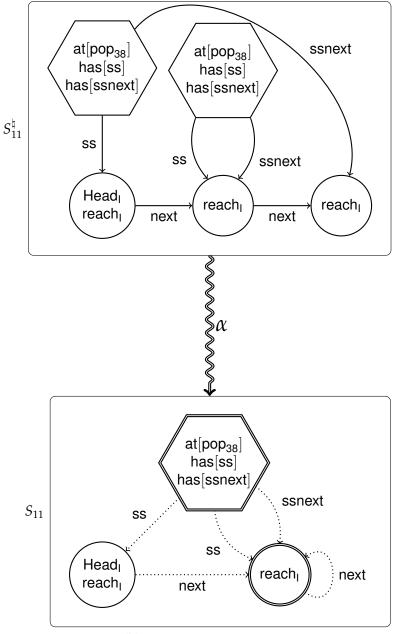

| 7.1 | Instrumentation predicate structures                                                                                                                         |

|     | (a) Linear predicates                                                                                                                                        |

|     | (b) Geometric predicates                                                                                                                                     |

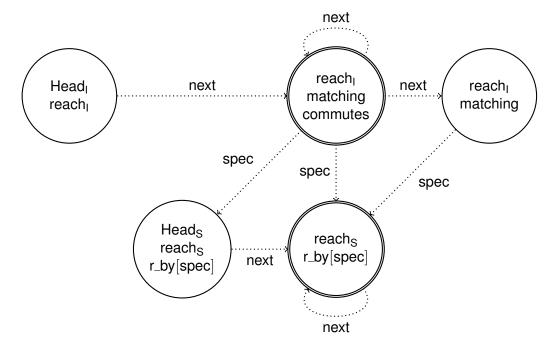

| 7.2 | Transitions of stack model                                                                                                                                   |

| 7.3 | Update actions used in stack model                                                                                                                           |

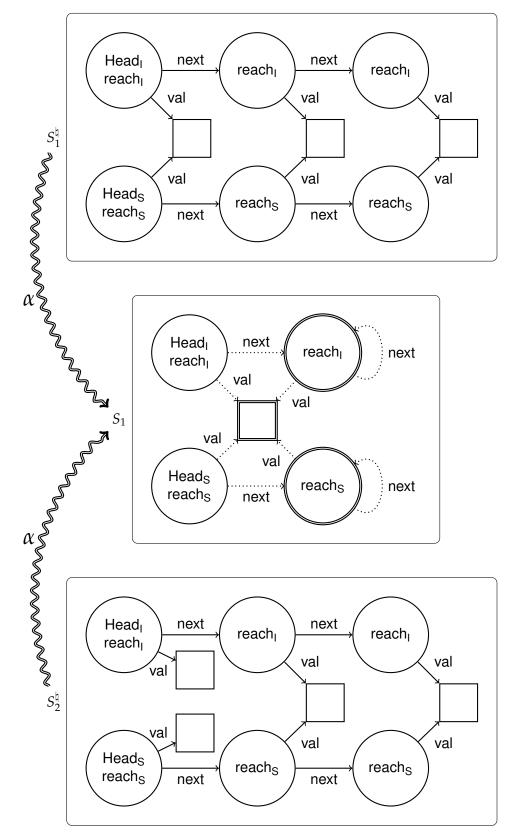

| 7.4 | Canonical abstraction of two lists: the property of matching                                                                                                 |

|     | values is lost                                                                                                                                               |

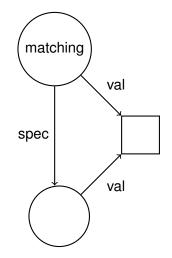

| 7.5 | Stack specification update operations, incorporating the spec                                                                                                |

|     | relation                                                                                                                                                     |

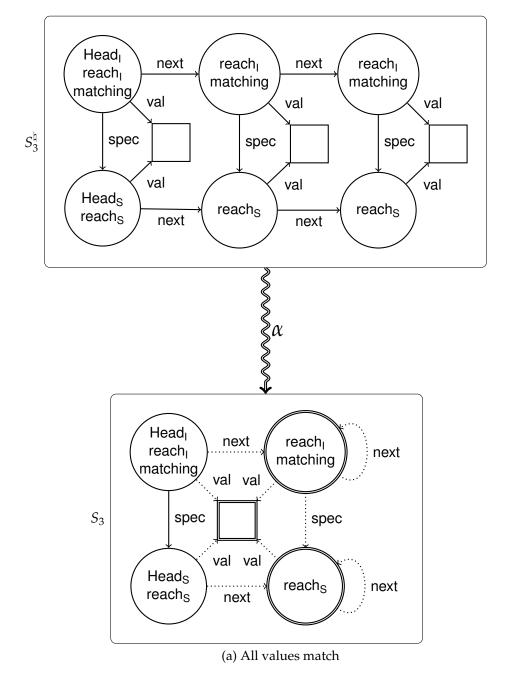

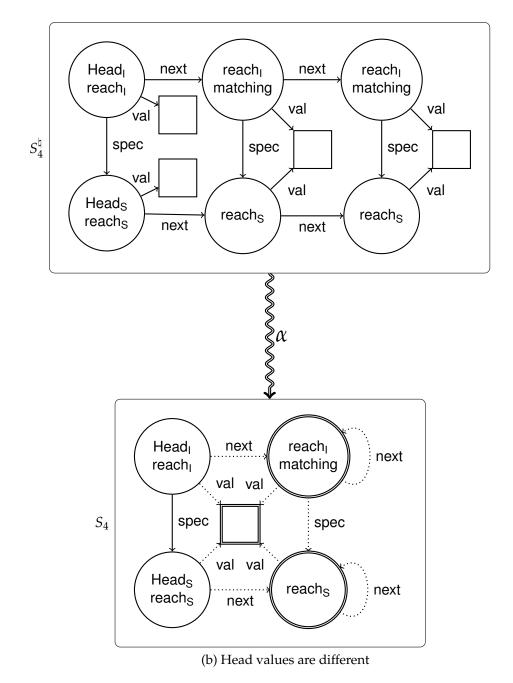

| 7.6 | Canonical abstraction of stack lists using the predicate matching:                                                                                           |

|     | the property of matching values is retained                                                                                                                  |

xiv

|             | () A11 1 (1                                                            | 1 - 0 |

|-------------|------------------------------------------------------------------------|-------|

|             | (a) All values match                                                   |       |

|             | (b) Head values are different                                          | . 153 |

| 7.7         | Canonical abstraction with "crossed" <b>spec</b> predicates: the       | 155   |

| 70          | property of ordered values is lost                                     | . 155 |

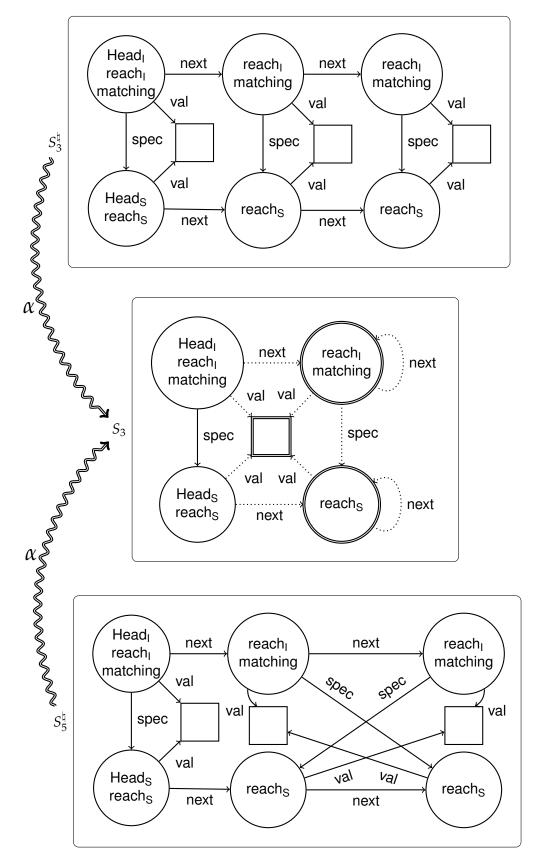

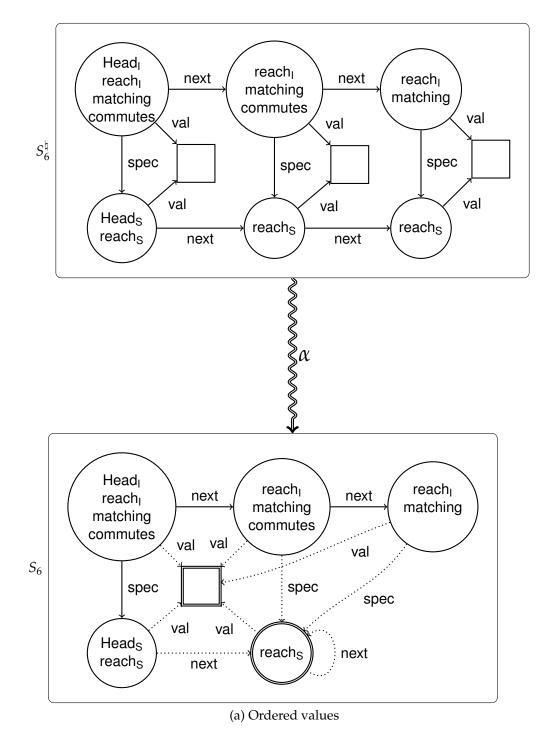

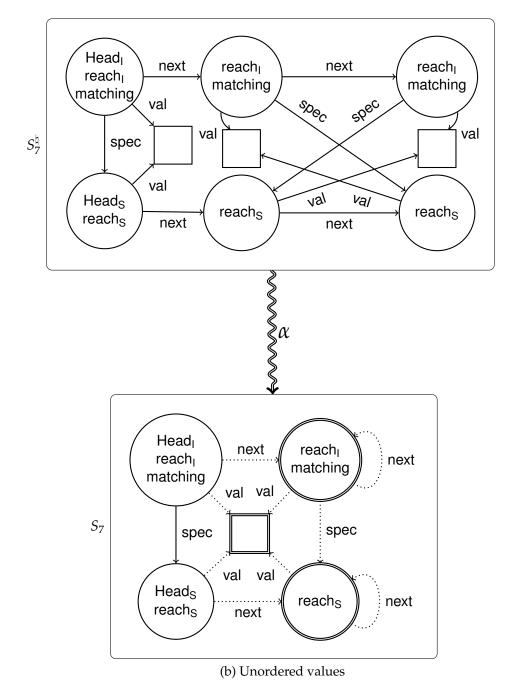

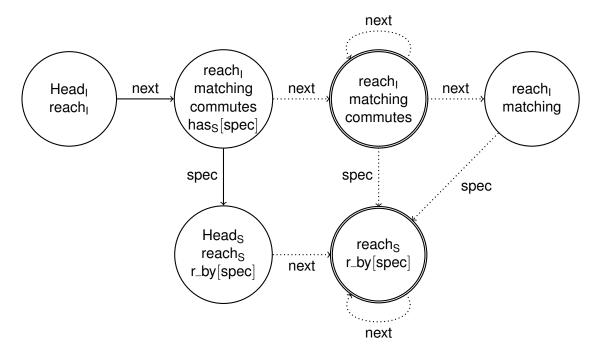

| 7.8         | Canonical abstraction using the commutes predicate: the                | 1     |

|             | property of ordered values is retained                                 |       |

|             | (a) Ordered values                                                     |       |

| 70          | (b) Unordered values                                                   | . 158 |

| 7.9         | In between the implementation and specification push up-               |       |

|             | dates the old implementation head node is abstracted with              | 150   |

| <b>F</b> 10 | the list body.                                                         | . 159 |

| 7.10        | With the has <sub>S</sub> [spec] predicate the old implementation head | 1.0   |

| <b>-</b> 11 | node is distinguished.                                                 | . 160 |

| 7.11        | I                                                                      | 1 ( 0 |

| <b>F</b> 10 | fields' values are lost                                                | . 163 |

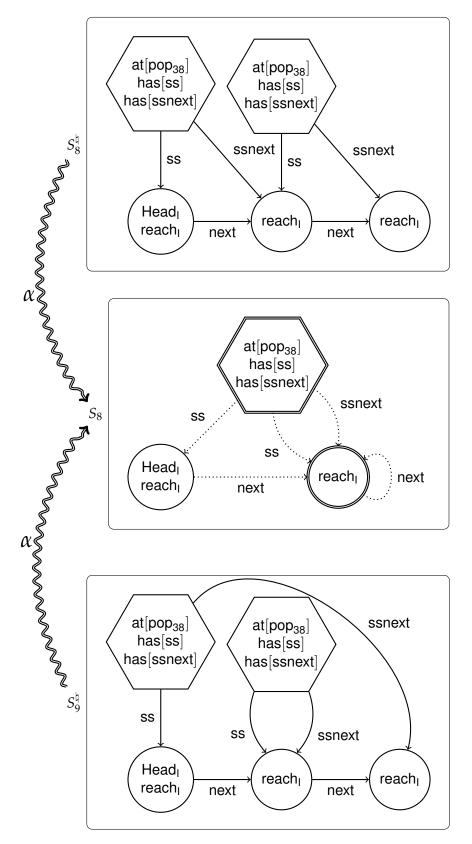

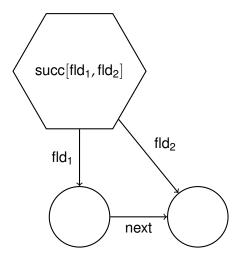

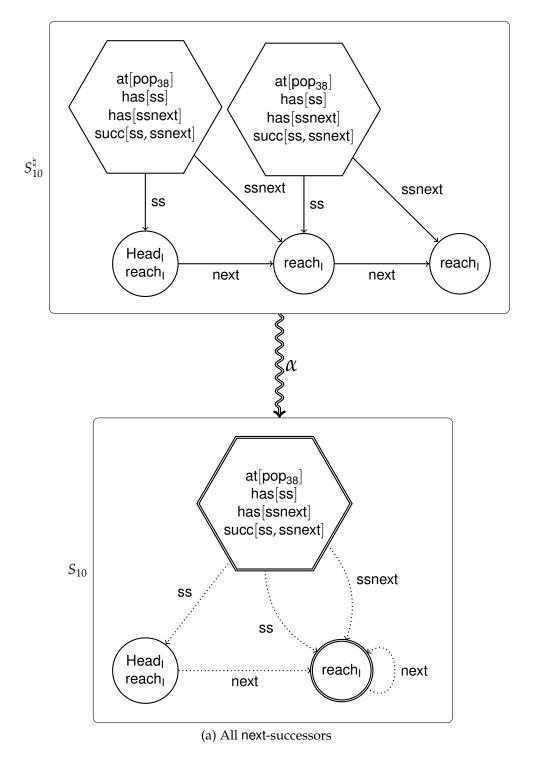

| 7.12        | Canonical abstraction using the succ[ss, ssnext] predicate:            | 1/5   |

|             | the relationships between fields' values are retained                  |       |

|             | (a) All next-successors                                                |       |

| <b>F</b> 10 | (b) None next-successors                                               |       |

|             | Initial state of the stack model (plain)                               |       |

|             | Initial state of the stack model (with "garbage" nodes)                |       |

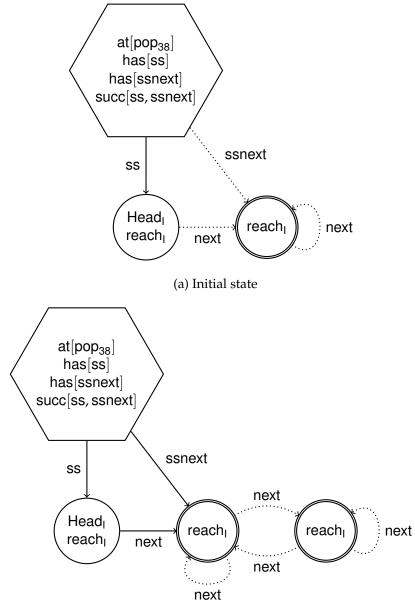

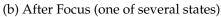

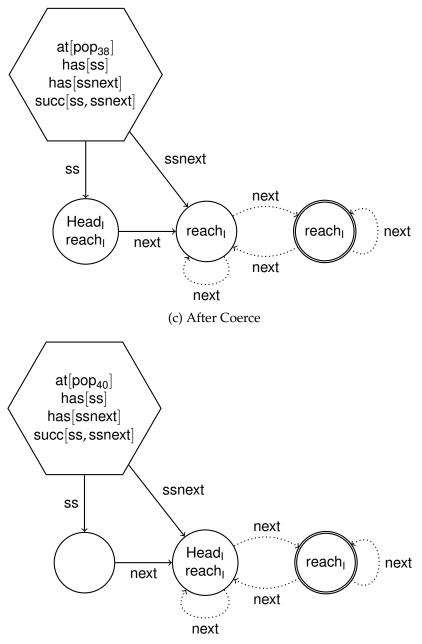

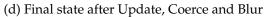

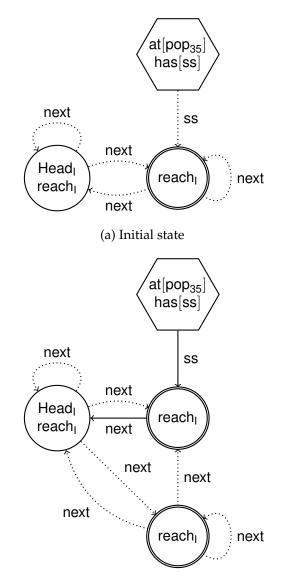

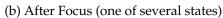

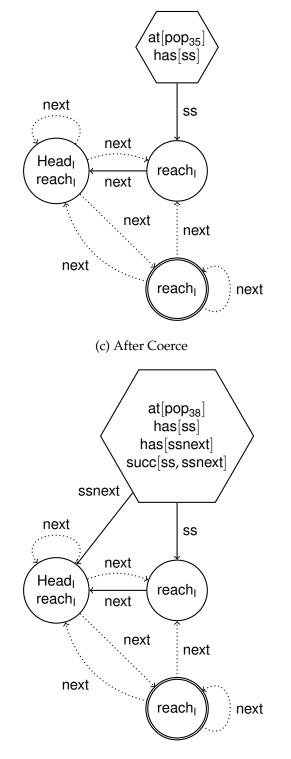

| 7.15        | Steps of a Pop update transition                                       |       |

|             | (a) Initial state                                                      |       |

|             | (b) After Focus (one of several states)                                |       |

|             | (c) After Coerce                                                       |       |

| - 4 4       | (d) Final state after Update, Coerce and Blur                          |       |

| 7.16        | Transition to an inconsistent state                                    |       |

|             | (a) Initial state                                                      |       |

|             | (b) After Focus (one of several states)                                |       |

|             | (c) After Coerce                                                       |       |

|             | (d) After Update and Coerce                                            |       |

| - 4 -       | (e) Final state, after Blur                                            |       |

|             | Incomplete matching triangle                                           |       |

|             | Transitions of stack model                                             |       |

| 7.19        | Transitions of queue models                                            |       |

|             | (a) Enqueue operation                                                  |       |

|             | (b) Original dequeue operation                                         |       |

|             | (c) Simplified dequeue operation                                       |       |

| 7.20        | Additional update operations used in queue models                      | . 192 |

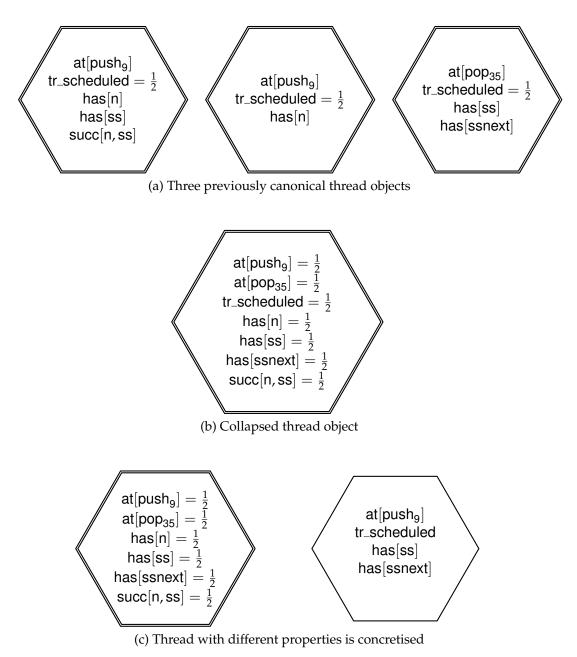

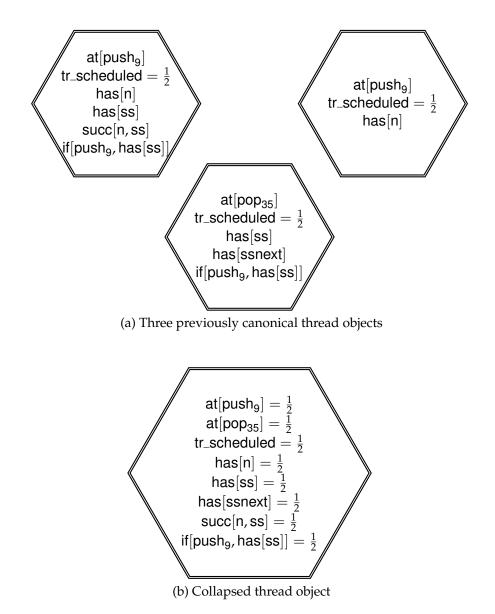

| 8.1 | Collapsing threads: loss of precision                              |

|-----|--------------------------------------------------------------------|

|     | (a) Three previously canonical thread objects                      |

|     | (b) Collapsed thread object                                        |

|     | (c) Thread with different properties is concretised 201            |

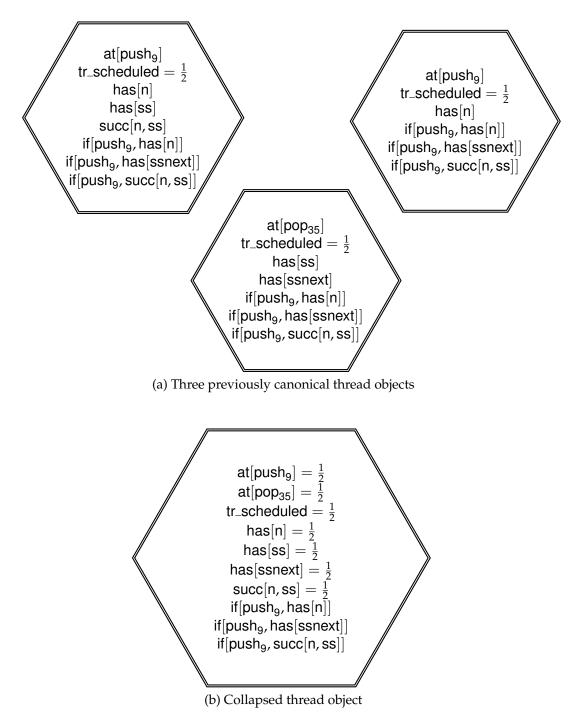

| 8.2 | Collapsing threads: properties preserved with soft invariants 203  |

|     | (a) Three previously canonical thread objects                      |

|     | (b) Collapsed thread object                                        |

| 8.3 | Collapsing threads: soft invariant for non-invariant property 204  |

|     | (a) Three previously canonical thread objects 204                  |

|     | (b) Collapsed thread object                                        |

| 8.4 | Concretised thread object to be sharpened                          |

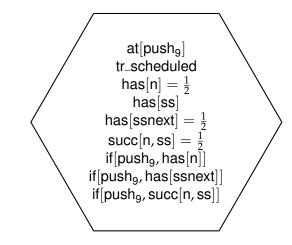

| 8.5 | Property of null equivalence is lost when threads are collapsed208 |

|     | (a) Before collapse                                                |

|     | (b) After collapse                                                 |

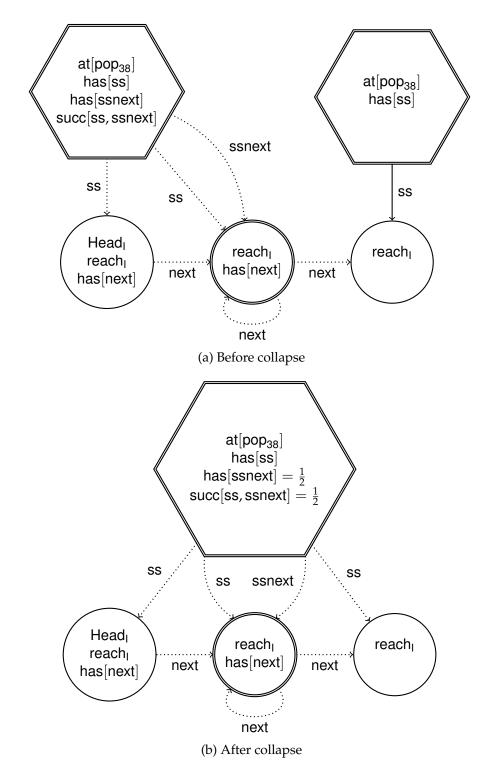

| 8.6 | Soft invariant instrumentation predicates for interleaving         |

|     | locations $\ldots$ $\ldots$ $\ldots$ $211$                         |

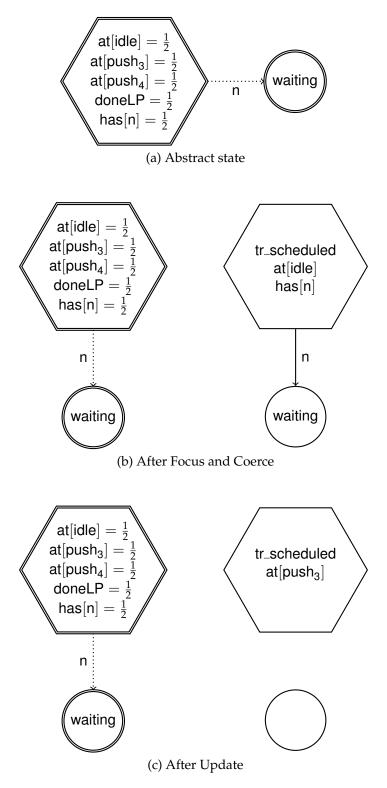

| 8.7 | Concretising an unreachable state                                  |

|     | (a) Abstract state                                                 |

|     | (b) After Focus and Coerce                                         |

|     | (c) After Update                                                   |

| 8.8 | Transitions of queue models                                        |

|     | (a) Enqueue operation                                              |

|     | (b) Original Dequeue operation                                     |

|     | (c) Simplified Dequeue operation                                   |

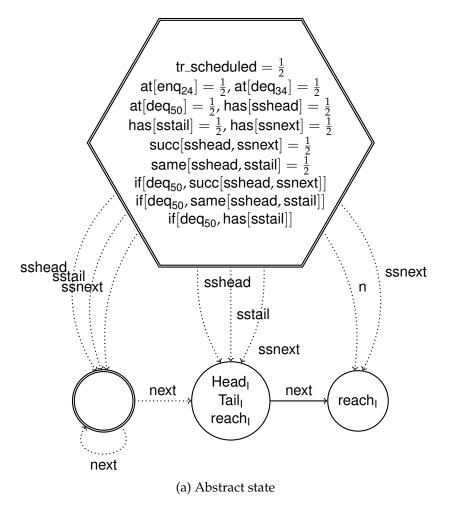

| 8.9 | Snapshot order not preserved                                       |

|     | (a) Abstract state                                                 |

|     | (b) After Focus and Coerce                                         |

xvi

## List of Tables

| 4.1  | Example integrity rules                                           |  |  |

|------|-------------------------------------------------------------------|--|--|

| 4.2  | Example instrumentation predicates                                |  |  |

| 6.1  | Minimum parameters for counterexamples to linearisability 122     |  |  |

| 6.2  | Treiber Stack Bounded Verification                                |  |  |

| 6.3  | MS Queue Bounded Verification                                     |  |  |

| 6.4  | DGLM Queue Bounded Verification                                   |  |  |

| 6.5  | LMS Queue Bounded Verification                                    |  |  |

| 6.6  | Treiber Stack Bounded Verification With Symmetry Reduction 128    |  |  |

| 6.7  | Minimum parameters for counterexamples to nonblocking             |  |  |

|      | properties                                                        |  |  |

| 6.8  | Treiber Stack Bounded Verification                                |  |  |

| 6.9  | MS Queue Bounded Verification                                     |  |  |

| 6.10 | DGLM Queue Bounded Verification                                   |  |  |

| 6.11 | LMS Queue Bounded Verification                                    |  |  |

| 7.1  | Stack verification results                                        |  |  |

| 7.2  | Canonical thread objects in unscheduled abstract stack states 181 |  |  |

| 7.3  | Stack analyses using isomorphic state comparisons 182             |  |  |

| 7.4  | Comparison with TVLA 2                                            |  |  |

| 7.5  | Stack analyses with unnecessary referenced-by instrumen-          |  |  |

|      | tation predicates                                                 |  |  |

| 7.6  | Stack analyses with a pure initial state                          |  |  |

| 7.7  | Stack analyses with named threads                                 |  |  |

| 7.8  | Stack verification results for bounded threads                    |  |  |

|      | (a) Resources                                                     |  |  |

|      | (b) Statespace                                                    |  |  |

| 7.9  | Stack verification results with no partial order reduction 187    |  |  |

| 7.10 | Queue verification results                                        |  |  |

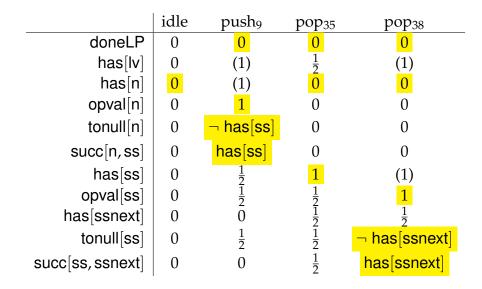

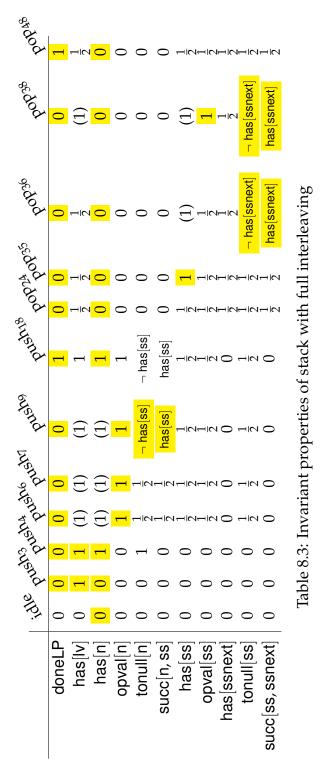

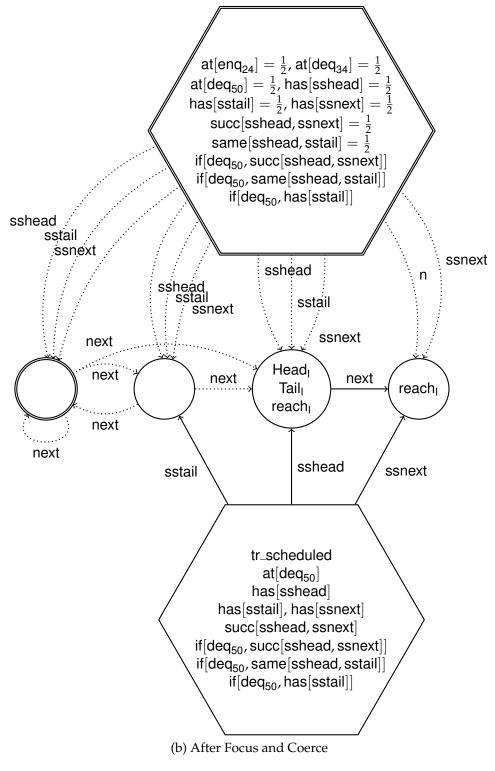

| 8.1                                                  | .1 Invariant properties of stack model with restricted inter-       |  |  |  |

|------------------------------------------------------|---------------------------------------------------------------------|--|--|--|

|                                                      | leaving                                                             |  |  |  |

| 8.2                                                  | Stack verification results for restricted interleaving 214          |  |  |  |

|                                                      | (a) Resources                                                       |  |  |  |

|                                                      | (b) Statespace                                                      |  |  |  |

| 8.3                                                  | Invariant properties of stack with full interleaving 215            |  |  |  |

| 8.4                                                  | 4 Stack verification results for full interleaving                  |  |  |  |

|                                                      | (a) Resources                                                       |  |  |  |

|                                                      | (b) Statespace                                                      |  |  |  |

| 8.5                                                  | 5 Stack verification results for full interleaving with extra pred- |  |  |  |

|                                                      | icates                                                              |  |  |  |

|                                                      | (a) Resources                                                       |  |  |  |

|                                                      | (b) Statespace                                                      |  |  |  |

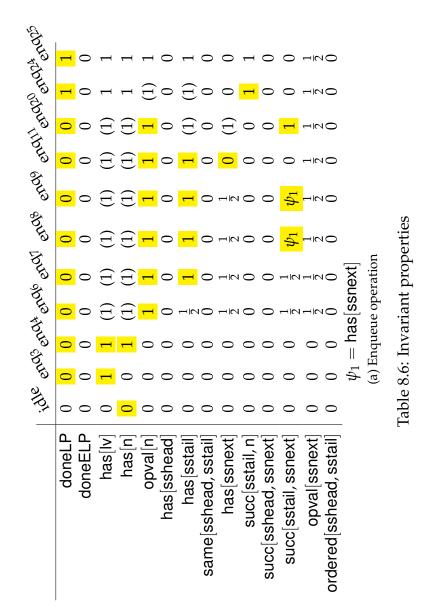

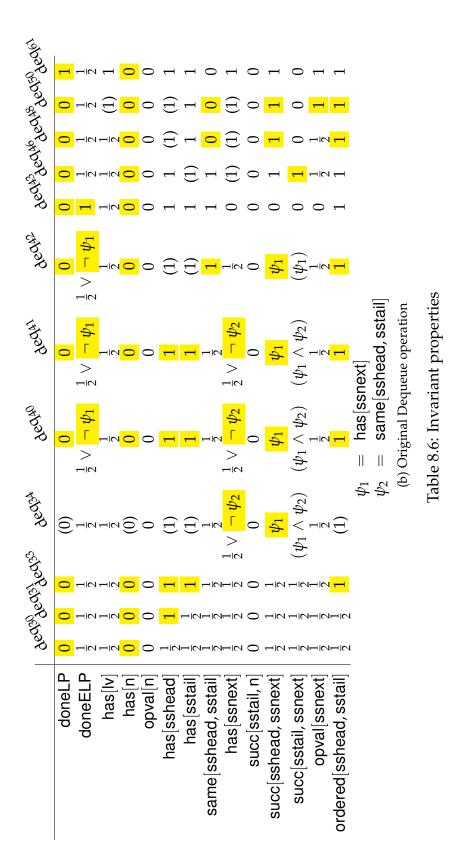

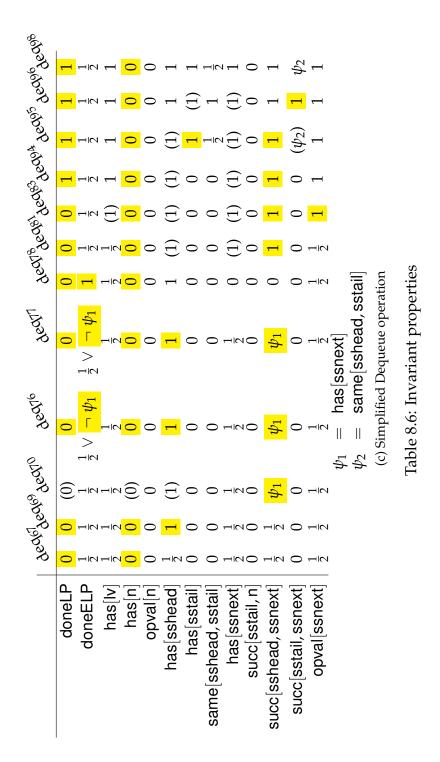

| 8.6                                                  | Invariant properties                                                |  |  |  |

|                                                      | (a) Enqueue operation                                               |  |  |  |

|                                                      | (b) Original Dequeue operation                                      |  |  |  |

|                                                      | (c) Simplified Dequeue operation                                    |  |  |  |

| 8.7                                                  | Queue verification results for restricted interleaving 230          |  |  |  |

| 8.8 Queue verification results for full interleaving |                                                                     |  |  |  |

|                                                      | (a) Resources                                                       |  |  |  |

|                                                      | (b) Statespace                                                      |  |  |  |

|                                                      |                                                                     |  |  |  |

xviii

### Chapter 1

### Introduction

In this thesis we investigate ways in which certain types of concurrent data structures can be verified using the formal technique called model checking.

We are interested in data structures within the *shared memory* concurrency paradigm, where a collection of threads communicate by reading and writing to a shared pool of memory. For correctness, we desire the algorithms to satisfy the safety property linearisability [Herlihy and Wing, 1990], and say that a data structure is *linearisable* if (roughly speaking) any execution has an equivalent execution in a given sequential specification (see Section 2.2). We also desire the algorithms to satisfy one of a number of progress properties, collectively known as *nonblocking* properties, that specify how threads can affect each other's behaviour when there is contention for shared resources.

#### 1.1 Nonblocking Concurrency

It is easy for concurrent threads to interfere with one another, causing *race conditions*. This can be avoided by synchronising threads using locks, which permit only one thread at a time to access some or all of the shared memory. However, locks have a number of issues that can affect their efficiency and scalability. Alternatively, it is possible to design so-called *nonblocking* algorithms that do not use locks, and that tend to scale much better [see, e.g. Greenwald and Cheriton, 1996; Michael and Scott, 1998]. However, as may be expected, they are also harder to design and reason about; many papers have been published containing algorithms with bugs

[e.g. Stone, 1990, 1992; Massalin and Pu, 1991; Valois, 1994, 1995; Detlefs et al., 2000; Shann et al., 2000; Tsigas and Zhang, 2001], some with pseudo-mathematical 'proofs'.

A number of general methods have been proposed to construct nonblocking implementations from sequential [Alemany and Felten, 1992; Barnes, 1993; Herlihy, 1993; LaMarca, 1994] and lock-based [Prakash et al., 1991; Turek et al., 1992] ones but the performance of the resulting algorithms is very poor compared with the corresponding lock-based algorithms. Also, some promising efforts have been made towards refinementbased methods that produce correct implementations by construction [Abrial and Cansell, 2005; Groves and Colvin, 2006; Groves, 2008a,b; Dongol and Mooij, 2008; Dongol and Hayes, 2009].

A number of approaches have been employed for constructing deductive proofs of the correctness of nonblocking data structures using theorem provers [Doherty et al., 2004b; Gao and Hesselink, 2004; Gao et al., 2004, 2005; Colvin et al., 2005, 2006; Colvin and Groves, 2005, 2007; Derrick et al., 2007, 2008; Colvin and Dongol, 2007, 2009; Doherty and Moir, 2009; Doherty, 2010]. Verifications by theorem provers can, however, be difficult and time-consuming. Furthermore, if a proof attempt has stalled it is not always easy to tell whether it is due to a bug in the algorithm or simply inexperience or mistakes on the part of the user [Doherty, 2003].

Some work has also begun using automated decision procedures for separation logic [Reynold, 2002]. Preliminary results are promising [Vafeiadis, 2007, 2009], but the method is currently only applicable to a small range of algorithms.

#### **1.2 Model Checking**

Model checking is an automated formal verification technique that works by exploring the entire state space of a finite-state system  $\mathcal{M}$ , checking a specification property  $\varphi$  (traditionally formalised in a temporal logic). Thus, it is able to determine the satisfiability of the property in the system  $(\mathcal{M} \models \varphi)$ , returning "yes" if it is true, and "no" otherwise, along with a counterexample — an execution trace leading from an initial state to an error state (for safety properties) or an infinite loop (for progress properties) where the property is false.

Sometimes a system under consideration cannot be directly examined by a model checker — either it has an infinite number of states, or the representation of the finite state-space exceeds the finite memory resources available. Technological advances (if it is possible to wait for their arrival) and distributed model checking techniques [e.g. Grumberg, 2002b; Melatti et al., 2006] may somewhat alleviate the latter situation by increasing the memory resources available, but this is offset by the state explosion problem — a linear increase in the number of concurrent threads, or any other parameter, results in an exponential increase in the state space. In both situations it may be possible to construct a (smaller) finite-state abstract system that preserves the property of interest. The framework of abstract interpretation [Cousot and Cousot, 1977, 1979] enables an abstraction on states to be used to construct an abstract system that preserves a particular temporal logic.

The limitation of model checkers to finite state systems prevents them from being applied directly to general representations of concurrent data structures. These data structure algorithms typically have three unbounded parameters as:

- there is no limit on the number of threads present;

- there is no limit on the size of the data structure (length of the list, etc.); and

- data values may have an infinite (e.g. integer) type.

Thus they must be considered as infinite state systems.

#### **1.3 Bounded Verification**

One way of analysing concurrent data structures using model checking is to construct a finite model with bounds on the parameters. This approach has been used in an ad hoc way by a number of authors [e.g. Harris, 2001; Fraser, 2003; Burckhardt et al., 2006, 2007; Colvin et al., 2006; Lamport, 2006; Fraser and Harris, 2007]. However, whilst it is a good approach for finding bugs, if no bugs are found it does not necessarily give any indication of the correctness of the algorithm.

'Folk wisdom' holds that most bugs will appear in small instances of systems [see, e.g. Jackson and Damon, 1996; Marinov et al., 2003; Dolby et al., 2007; Jackson, 2012; Oetsch et al., 2012] This suggests that verifying bounded models up to a "reasonable" size would give some confidence in the correctness of the unbounded model. Several questions arise at this point:

- 1. What size instances would need to be verified in order to give a reasonable level of confidence in an algorithm?

- 2. What size instances are needed to trigger known bugs in existing algorithms?

- 3. Is this approach equally applicable to both linearisability and the nonblocking properties?

- 4. Is this approach worth doing before, or instead of, a full verification (using a theorem prover, model checker with abstraction, etc.)?

These questions have not been comprehensively explored in the literature. In this thesis we aim to address all of the questions, by presenting a range of case studies — of both correct and incorrect algorithms — checking linearisability and nonblocking properties.

#### **1.4 Unbounded Verification**

A powerful approach for verifying large or infinite state systems with a model checker is to construct a finite state abstraction that *preserves* the property of interest, i.e. such that the property holds in the original if it holds in the abstraction. Some information in the states is made less precise, allowing each abstract state to represent (infinitely) many concrete states.

Since the verification of parametrised systems is undecidable in general [Apt and Kozen, 1986], it is inevitable that any abstraction techniques will be limited in applicability. Many such techniques have been proposed for parametrised systems (see Section 3.5), though most only consider one parameter (generally the number of threads) so are not applicable to concurrent data structures.

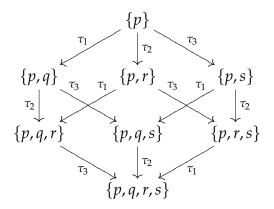

The more general technique of canonical abstraction [Sagiv et al., 2002] is able to be applied to concurrent data structures, as it puts a finite bound on the number of possible abstract states. Canonical abstraction represents abstract states as 3-valued logical structures over a fixed finite set of predicates. It is possible to trivially abstract any system to an abstract system consisting of a single state, which (perhaps spuriously) fails every

property. Thus, the principal problem is not whether an abstraction can be constructed, but whether we can construct an abstraction that is detailed enough to allow the specified property to be verified, but not so detailed that it is too large to be fully examined. This involves choosing the right balance of formulas to be represented by additional *instrumentation* (or *derived*) predicates, which are defined in terms of the other core predicates.

There are several questions that can be asked about canonical abstraction in this context:

- 1. Can canonical abstraction be used to verify linearisability for nonblocking data structures, with unbounded instances of all three parameters?

- 2. Can canonical abstraction be used to verify nonblocking properties for concurrent data structures, with unbounded instances of all three parameters?

- 3. If so, for either of the above, are the abstractions efficient (i.e. are they small enough to enable practical verification)? If not, is it possible to improve them?

In this thesis I will answer the first question in the affirmative, at least for linked list based stacks and queues. Independently, other researchers have used canonical abstraction to achieve the same result, i.e. verify linearisability for linked list based stacks and queues with unbounded lists and data values but bounded threads [Amit et al., 2007], and then for unbounded threads also [Berdine et al., 2008]. One of the principal distinctions is that these add additional layers on top of canonical abstraction to achieve the results, whilst my approach is achievable purely within canonical abstraction.

I will also address the third question, proposing a technique to more effectively abstract threads than has been done before in canonical abstraction.

The second question is left for future work.

#### 1.5 Outline

The remainder of the thesis is divided into three parts. The first part contains background material. Chapters 2 and 3, covering nonblocking

concurrent data structures and model checking, respectively, are utilised throughout. Chapter 4, covering canonical abstraction, is utilised in Part III.

The second part investigates modelling and testing nonblocking data structures using model checking. Chapter 5 details how to

- represent nonblocking data structure algorithms,

- specify the safety property linearisability, and

- specify the nonblocking progress properties wait-, lock- and obstructionfreedom

for model checking. Chapter 6 details the results of bounded verification for a range of nonblocking data structures.

The third part investigates verifying nonblocking data structures using model checking. Chapter 7 details how linearisability of linked list based nonblocking data structures can be verified using canonical abstraction. Chapter 8 details a method for more efficiently using canonical abstraction by abstracting all of the threads together.

Finally, Chapter 9 is the conclusion, in which we directly address the questions raised in this chapter.

# Part I Background

### Chapter 2

### **Nonblocking Data Structures**

In this chapter we introduce nonblocking data structures as used throughout the thesis. Section 2.1 discusses the general representation of concurrent data structures used. Section 2.2 discusses the safety property linearisability, which relates a concurrent algorithm to a sequential specification. Section 2.3 discusses the use and problems of mutual exclusion to synchronise access to shared information. Section 2.4 introduces the progress properties wait-freedom, lock-freedom and obstruction-freedom (collectively "nonblocking properties"<sup>1</sup> that can apply to concurrent algorithms that do not employ mutual exclusion, whilst Section 2.5 discusses some atomic operations that can be used to achieve concurrent synchronisation with these properties. Finally, Section 2.6 describes two data structure algorithms that will be used as examples.

#### 2.1 Concurrent Data Structures